# Reference Guide For D–Bug12 Version 4.x.x

A Debug Monitor

For

The MC9S12Dx256, MC9S12A256, MC9S12Dx128, MC9S12H256 &

MC9S12A128 Microcontrollers

Written By

Gordon Doughman

Field Applications Engineer

Software Specialist

# 1.0 Introduction

D–Bug12 has undergone considerable revision since the introduction of version 1.0.x for the M68HC812A4 EVB and version 2.x.x for the MC68HC912B32 EVB. Version 4.x.x of D–Bug12 was developed for the MC9S12DP256 to provide an economical yet powerful debugging tool that can be utilized to develop M68HC12 applications or simply to evaluate the M68HC12 architecture. The MC9S12DP256 was chosen for this latest version of D-Bug12 to provide more Flash memory for additional features and programming support for new M68HC12 Flash memory technologies. While this new version has the capability to run as a simple ROM monitor in an MC9S12DP256 EVB, most of the improvements are related to D–Bug12's operation in 'POD' mode. In this operating mode, D–Bug12 communicates with a target M68HC12 microcontroller through the Single–Wire Background Debug Mode (BDM) Interface to allow true emulation of an application in the target microcontroller's operating environment.

Target MCU Flash and EEPROM programming support has been dramatically improved, especially for those family members utilizing their on-chip PLLs. D-Bug12 now supports buffered, interrupt driven SCI communications utilizing XOn/XOff software handshaking for all serial communications. This feature allows D-Bug12 to continue receiving S-Record data from the host computer while it is sending data from the previously received S-Record to the target MCU.

Version 4.x.x of D-Bug12 utilizes the same variable speed BDM communications primitives as version 2.1.x allowing the target MCU to be operated with a bus clock between 16.384 kHz and the bus frequency of the MC9S12DP256 on the EVB (normally 24.0 MHz).

**Note:** It is strongly recommended that current D-Bug12 users read Section 2 and 3 of this reference guide. Section 2 explains the new features in version 4.x.x. Section 3 explains the new requirements for the terminal emulator program used with D-Bug12.

### 2.0 New Features

In addition to several new commands that have been added to D-Bug12, many of the it's commands have been updated or enhanced. The following sections describe the updated features of D-Bug12's command set.

- Supports on-chip hardware breakpoint modules. Including the UDR HC12 and HCS12 products providing two program only hardware breakpoints.

- EVB or target hardware breakpoints are enabled by default. Software breakpoints may be enabled by using the USEHBR command.

- FBulk command supports Motorola's newly specified erase pulse timing of 10 mS for UDR M68HC12 devices.

- Improved target memory read and write routines supporting aligned word access of 16-bit wide memory and peripherals.

- D–Bug12 utilizes the XIRQ interrupt input for a program abort function when operating in EVB mode.

- Maximum S-Record code/data field length was increased to 64 bytes to support programming of M68HC12 family members utilizing SST Flash.

- Support for all MC9S12DP256 interrupt vectors when operating in EVB mode.

- Improved VERF command reports the target & S-Record data when two memory locations don't match.

- Arithmetic expressions involving CPU register names and numeric constants are permitted in place of a simple hexadecimal address for most commands.

- The TCONFIG command can be used to configure target hardware, typically I/O ports that control VFP circuitry, before erasing or programming target Flash memory.

- UPLOAD command improved to allow S-Record target memory display for M68HC12 family members containing more than 64K of flash memory.

- DEVICE command can no longer be used to specify a new target MCU device.

- Disassembler now displays indexed addressing modes using the program counter with a 5-, 9-, or 16-bit offset as: <AbsoluteAddress>, PCR.

- Target EEPROM may be programmed using the LOAD command without changing D-Bug12's baud rate.

- For devices containing more than 64K of address space, the value of the PPAGE register can be changed using the PP command.

- Improved support for expanded addressing for HC12 and HCS12 devices containing more than 64K of program memory.

- The PCALL command, similar in operation to the CALL command, was added to allow subroutines ending with the RTC instruction to be executed from the command line.

- The FLOAD, VERF and LOAD commands have been enhanced to accept either linear or 'banked' S-Records.

# 2.1 Hardware Breakpoint Support

Earlier versions of D–Bug12 supported 10 software breakpoints allowing developers to halt program execution on instruction opcode boundaries. Unfortunately, the placement of software breakpoints are restricted to programs that reside in alterable memory. This restriction is not a problem for small programs placed in the on-chip RAM or EEPROM when operating the EVB in EVB mode. However, when the EVB is utilized in POD mode to test and debug code in a target M68HC12's Flash, software breakpoints cannot be used.

To facilitate debugging in an M68HC12's on-chip flash, many M68HC12 family members include an on-chip hardware breakpoint module. D–Bug12 supports the hardware breakpoint module by providing two hardware breakpoints in place of the 10 software breakpoints. Even though the breakpoint module is capable of providing data access breakpoints, D–Bug12 currently supports only the module's dual address program breakpoint operating mode. In this operating mode, the hardware breakpoints utilize the CPU12's instruction tagging mechanism. Much like software breakpoints, this restricts the placement of the hardware breakpoints to the address of an instruction opcode.

The hardware breakpoints may be used in both POD and EVB operating modes. Utilizing the hardware breakpoints in EVB mode is especially important when developing code in the on-chip EEPROM. The hardware breakpoints prevent D–Bug12 from erasing and reprogramming the EEPROM each time an instruction is traced or breakpoints are placed in memory.

D-Bug12's 10 software breakpoints are still available to the programmer, however, the default operating mode uses the two hardware breakpoints. Refer to the USEHBR command documentation for details on changing the breakpoint operating mode.

# 2.2 FBULK Erase Pulse Time Reduced for UDR Flash Devices

Motorola has recently made a change to the erase pulse timing specification, tepulse, reducing it from a nominal value of 100 mS to a nominal value of 10 mS. The FBULK command has been modified to reflect this change. This change applies only to supported 'UDR 1.5T' family Flash devices. M68HC12 family devices utilizing the SST Flash technology ('A' suffix devices) and the HCS12 devices are supported with the appropriate erase and programming algorithms.

# 2.3 Additional Flash Programming Support

The FLOAD, FBULK, VERIFY and DEVICE commands have been enhanced to support on-chip Flash programming for additional M68HC12 family members - the MC68HC912D60, MC68HC912DA/DG128, MC68HC912GA32, MC68HC912KD/K128, MC68HC912DP256 and the MC68HC912DT128A. In addition, the LOAD command, which supports loading of S-Records into RAM, supports the extended memory space of the MC68HC812A4. For details of the S-Record format required for parts supporting greater than 64K bytes of program memory, refer to the LOAD, FLOAD and VERIFY commands.

**Note:** The 'A' suffix devices, such as the MC68HC912DT128A, utilize Flash memory technology licensed from SST Corporation. Unlike the 'UDR 1.5T' that may be programmed a byte or aligned word at a time, the SST Flash must be programmed 64 bytes (32 aligned words) at a time. To program 'A' series devices requires S-Records that have a code/data field of EXACTLY 64 bytes and the load address must begin on a 64 byte boundary. For compilers or assemblers that do not have the capability to produce S-Records in this format, a utility named SRecCvt.exe supplied with D-Bug12, may be used to reformat any S-Record file.

Note: The HCS12 devices, such as the MC9S12DP256, utilize Flash memory technology licensed from SST Corporation. Unlike the 'UDR 1.5T' that may be programmed a byte or aligned word at a time, the SST Flash must be programmed an aligned word at a time. Programming these devices requires S-Records containing a code/data field consisting of an even number of bytes. In addition, the load address must begin on an even byte boundary. For compilers or assemblers that do not have the capability to produce S-Records in this format, a utility named SRecCvt.exe supplied with D-Bug12, may be used to reformat any S-Record file.

**Note:** Please refer to the section titled "FLOAD, LOAD and VERIFY S-Record Format" at the end of this document for a complete description of the S-Record Format utilized by these commands for M68HC12 devices supporting more than 64K bytes of memory.

# 2.4 16-bit Aligned Target Memory Access Supported

All versions of D–Bug12 prior to 2.1.x access memory a byte at a time through low–level drivers. Because all on-chip memory modules support byte access, utilizing this method simplified the low level driver code. However, this access method presents some potential problems for 16-bit registers that reside in the on-chip peripherals. Because the data bus connection to the on-chip peripherals is 16-bits wide, with a few exceptions, the peripherals are designed in such a way that 16-bit registers must be read or written with a single 16-bit access to ensure data coherency.

D–Bug12's low level memory access drivers have been rewritten to perform aligned word reads whenever possible. For instance, if the Memory Modify Word (MMW) command is used with an even address, all reads and writes will be performed as aligned word accesses. However, if the MMW command is used with an odd address, each memory access will be performed as two individual byte read or write operations. Because the Memory Display commands (MD and MDW) always display an even multiple of 16 bytes, all memory read operations are performed as aligned word accesses.

# 2.5 XIRQ Interrupt Usable As Program Abort Input

When testing and debugging programs that reside in the internal RAM or EEPROM of the MC9S12DP256 when operating in EVB mode, it is possible for the program to become 'hung-up' and never return to the D-Bug12 prompt. In these cases, it is desirable to terminate user program execution and return control to D-Bug12. Unfortunately, pressing the reset switch, S1, causes a

reinitialization of D–Bug12 resulting in a complete loss of information about the state of the executing user code. D–Bug12 utilizes the XIRQ interrupt input to terminate the execution of a user program and return control to D-Bug12. Even though a program abort switch is not present on the MC9S12DP256 EVB, the XIRQ interrupt input (PE0) may be utilized for a program abort function. One side of a normally open, momentary contact push button can be wired to the XIRQ input, the other side of the push button should be wired to Vss.

Utilizing the program abort function will return control back to D–Bug12, displaying the CPU register contents at the point where the users program was terminated.

# 2.6 MC9S12DP256 Interrupt Vector Support

When D-Bug12 is operated in EVB mode, it provides default interrupt handlers for all of the on-chip peripherals. Version 4.x.x now fully supports the use of the MC9S12DP256 as a host CPU by providing default interrupt handlers for all of the MC9S12DP256's interrupt vectors.

# 2.7 Maximum S-Record Code/Data Field Length Increased

To support the programming of the M68HC12 'A' suffix devices that utilize Flash memory technology licensed from SST Corporation, the maximum S-Record code/data field length was increased to 64 bytes.

# 2.8 Improved VERF Command

In previous versions of D-Bug12, the VERF command terminated execution with an error message when target memory contents did not match the received S-Record. To improve support for debugging memory related problems, the VERF command now reports the S-Record address, S-Record data, Target memory address and target memory contents for **each** target memory location that does not match the S-Record contents.

# 2.9 Simple Arithmetic Expressions

Many of D-Bug12's commands accept one or more 16-bit hexadecimal addresses as command line parameters. To simplify the debugging process, these parameters may be supplied as a 16-bit hexadecimal number **or** a simple numeric expression. The simple numeric expression may consist of one or more CPU register names (PC, X, Y, SP, A, B or D) or numeric constants separated by the addition (+) or subtraction (–) operator. The numeric constants may be supplied in one of four number bases by using one of three number base prefix characters. In expressions, hexadecimal numbers must be preceded by the dollar sign character (\$), octal numbers must be preceded by the commercial at character (@) and binary numbers must be preceded by the percent character (%). Within expressions, numbers not preceded by one of the number base character designators is interpreted as a decimal number.

Using numeric expressions in command line parameters can be advantageous in a number of debugging circumstances. For example, when using the Trace command (T) to step through program code, it is often desirable to skip execution of subroutines that are known to function properly. This can be easily accomplished using a simple numeric expression in the operand field of the GoTill (GT) command, setting a temporary breakpoint at the instruction following a JSR. In this instance entering the command line GT PC+3 places a temporary breakpoint at the current location of the Program counter plus three, the length of the JSR instruction utilizing extended addressing. Obviously, JSR instructions using other addressing modes or BSR instructions would require an offset other than three.

Another important use of expressions in command line parameters is for examining data accessed with a reference to one or more of the CPU12's index address registers. This can be especially advantageous for instructions such as the MOVB or MOVW instructions where the data does not pass through one of the CPU registers. Consider the case where a MOVW instruction is used to move data from one data table to another utilizing accumulator offset indexed for both the source and destination address (MOVW A, X, B, Y). To examine or change the data at the destination address either before or after the execution of the MOVW instruction, entering the command line MMW Y+B would display the data at the destination address without having to perform any hexadecimal arithmetic. In a similar situation where data in a stack frame is accessed relative to the stack pointer, using an expression for the memory display (MD) or memory modify (MM) command line parameter can greatly simplify the task of examining passed parameters or local variables.

**Note:** Simple numeric expressions may not contain space characters.

# 2.10 TCONFIG Command

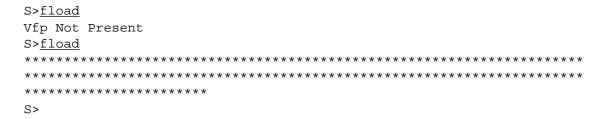

Some target systems contain their own VFP generation circuitry to allow in–circuit programming via CAN, J1850 or even the SCI. For these systems, it is desirable to utilize the target VFP generation circuitry for programming of the on-chip Flash rather than an externally supplied programming voltage. In most cases, the application of the target generated programming voltage to the VFP pin is controlled by one or more I/O pins of the target M68HC12. The TCONFIG command can be used to specify up to eight one byte values that will be written to the target memory just before the execution of the FBULK and FLOAD commands. For additional details on the syntax and features of the TCONFIG command please refer to the detailed command description in Section 5.

# 2.11 UPLOAD Command Improvements

In earlier versions of D-Bug12, the UPLOAD command did not support the display of memory contents for devices containing more than 64K of Flash memory. The UPLOAD command now supports devices containing more than 64K of Flash memory. In addition, a command line option has been added that allows the size of the S-Record code/data field to be specified. For additional details on the syntax and features of the UPLOAD command refer to the detailed command description in Section 5.

# 2.12 DEVICE Command Changes

Version 2.x.x of D-Bug12 allowed new MCU device definitions to be added to D-Bug12's device table. This feature was initially provided to allow support for devices that utilized the UDR 1.5T Flash technology with less than 64K of Flash memory. Because the M68HC12 family now utilizes four different Flash memory technologies and has planned devices with up to 256K of Flash memory, it is not practical to support new family members by simply defining new devices using the DEVICE command. Instead, the D-Bug12 device table contained in Flash and may not be altered. As new M68HC12 family members are developed, new versions of D-Bug12 will be released to support Flash and EEPROM programming of the new devices.

# 2.13 Disassembler Improvements

When writing position independent code, it is necessary to access global variables and/or data utilizing program counter relative indexed addressing. Earlier versions of D-Bug12 disassembled instructions using this form of indexed addressing as: <signed offset>, PC. This form of disassembly made debugging position independent code difficult because the signed offset to a memory location changes depending where it is referenced within a program. To make debugging position independent code easier, instructions using the program counter as an index register are now disassembled as: <AbsoluteAddress>, PCR. The absolute address is displayed as a four digit hexadecimal number preceded by a dollar sign (\$).

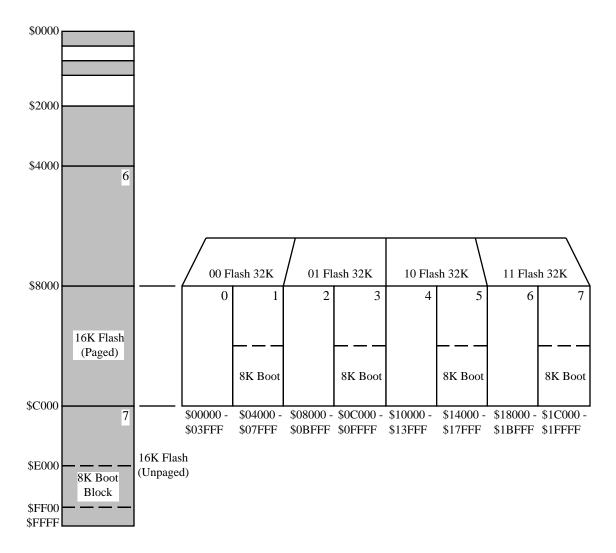

# 2.14 PP Command

The PPAGE register is present on M68HC12 family devices that have a program memory space greater than 64K. The PPAGE register, located in the I/O register block, is used in conjunction with the CALL and RTC instructions to address expanded program memory through the memory expansion window (\$8000 - \$BFFF). Because the PPAGE register is located at a different I/O register address in various M68HC12 family members, the PP command can be used to change its value. See Section 5 for a complete description of the PP command.

# 2.15 Expanded Addressing Support

D-Bug12 now fully supports the expanded address space of M68HC12 family members containing more than 64K of program memory. The display of register values now includes the PPAGE register if the selected device contains more than 64K of program memory. The new register display format is shown below. Note that the disassembly line displays the characters 'xx' in place of the PPAGE register value if the program counter value is outside the range of the PPAGE window (\$8000 - \$BFFF) indicating that the PPAGE register value is not pertinent to program execution in this memory range.

```

PP PC SP X Y D = A:B CCR = SXHI NZVC

30 C00A 4000 0000 0000 00:00 1101 0000

xx:C00A CF3FFF LDS #$3FFF

```

In addition to the new register display and disassembly format, the Go (G), GoTill (GT), ASM, BR and NOBR commands accept an additional address format that includes a PPAGE value. The expanded address format consists of an 8-bit PPAGE number and a 16-bit PPAGE window address separated by the colon character (':'). The general format of an expanded address is:

```

<PPAGENum>:<PPAGEWinAddr>

```

Both the PPAGE number and the PPAGE window address may consist of a simple expression. <PPAGENum> must be in a valid range for the selected device and <PPAGEWinAddr> must be an address in the PPAGE window (\$8000 - \$BFFF).

**Note:** Because the GoTill (GT), BR and NOBR commands involves setting breakpoints, the target MCU must contain a breakpoint module that supports the PPAGE number as part of the address comparison. The original UDR M68HC12 family members do not posses this capability. Alternatively, if the UDR target system contains RAM in place of the Flash (such as an EVS system), the GoTill (GT), BR and NOBR commands may be used in conjunction with software breakpoints (see the USEHBR command description in Section 5).

# 2.16 PCALL Command

The PCALL command is used to execute a subroutine ending with an RTC instruction, returning to the D-Bug12 monitor program when the final RTC of the subroutine is executed. For complete information, see the PCALL command description in Section 5.

# 2.17 FLOAD, VERF and LOAD command Enhancements

The FLOAD, VERF and LOAD commands have been enhanced to allow direct loading of 'banked' S-Records produced by some development tools. Please see the description of the FLOAD, VERF and LOAD commands for complete details on the additional features added to these commands.

# 3.0 Terminal Communications Setup

Version 4.x.x of D-Bug12 requires a host terminal program that supports XOn/XOff software handshaking for proper operation. Many popular terminal emulation programs for the Windows<sup>TM</sup> operating system meet this requirement. However, because the HyperTerminal terminal emulation program is supplied with Windows 95/98/NT it is recommended for use with D-Bug12. The factory configured default communications parameters used by D-Bug12 are 9600 baud, eight data bits, one stop bit, XOn/XOff handshaking and no parity.

When configured for EVB mode, the communications parameters will revert to the factory default settings whenever the board is powered down or reset. However, when operating the EVB in POD mode, baud rate changes made using the BAUD command are stored in the MC9S12DP256's on-chip EEPROM, making the entered baud rate the new default communication rate. If communication cannot be established with the EVB and random characters are displayed on the terminal screen, it is possible that the baud rate was changed to something other than the current settings of the terminal program.

If attempting communications at various baud rates does not result in D-Bug12's prompt being displayed, the EVB's on-chip EEPROM should be erased to reconfigure the baud rate to the factory default of 9600. This task can be accomplished by configuring the EVB for EVB mode, setting the terminal emulator program to 9600 baud and entering the BULK command on the command line. If communication cannot be established when the EVB is configured for EVB mode, check all communications and power connections to the EVB board.

# 3.1 Configuring HyperTerminal

The HyperTerminal terminal emulation program is supplied with Windows 95/98/NT and is recommended for use with D-Bug12 version 4.x.x. For those not familiar with HyperTerminal, this section describes the setup procedure necessary to use HyperTerminal with D-Bug12. For most Windows configurations, a short cut to the HyperTerminal program or the HyperTerminal folder can be found in the Start menu under Programs/Accessories/Communications. If a short cut for the HyperTerminal program or folder does not exist in the communications menu, use the Find item in the Start menu to search for the program.

After locating the HyperTerminal program or short cut icon, double click on the icon to start the program. When presented with the Configuration Dialog click cancel to dismiss the dialog box. From the **File menu** select **Properties**. Make sure that the **Connect To** tab is selected. From the **Connect using** drop down list, select a direct connection using one of the computers COM ports. After selecting the comport, click on the **Configure...** button to reveal the Properties Dialog. Use the drop down lists to set the baud rate to 9600 (factory default), one stop bit, no parity and XOn/XOff handshaking. Click the OK button in the Properties and connection dialog box to confirm the settings.

In the Call menu select the Call item to establish a connection through the selected COM port to the EVB. Pressing the reset button on the EVB should display one of the D-Bug12 sign-on messages and prompt. If nothing appears on the screen, check the connection between the computer and EVB to ensure that the EVB is connected to the proper serial port. If random characters appear on the screen, it is most likely that an incorrect baud rate was selected.

**Note:** Before selecting a new baud rate, HyperTerminal must be disconnected from the communication source by selecting **Disconnect** from the **Call** menu. Failure to disconnect from the communication source will cause HyperTerminal to ignore any new port settings.

# 4.0 Operating Modes

The D-Bug12 firmware has four operating modes controlled by the logic level present on the PAD0 and PAD1 pins at power up or reset. The operating modes for the four logic level combinations are presented in Figure 1.

| PAD1 | PAD0 | OperatingMode           |

|------|------|-------------------------|

| 0    | 0    | D-Bug12;EVB             |

| 0    | 1    | Jump to internal EEPROM |

| 1    | 0    | D-Bug12;POD             |

| 1    | 1    | SerialBootloader        |

Figure 1, D-Bug12's Operating Modes

# 4.1 EVB Mode

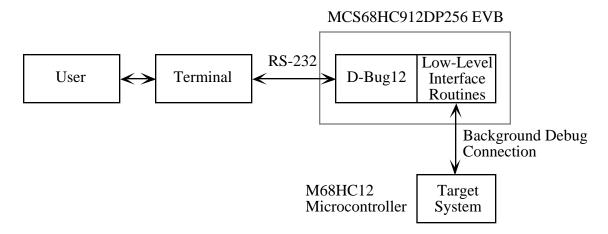

In D-Bug12's 'EVB' mode the monitor firmware operates as a ROM resident monitor/debugger executing from the MC9S12DP256's internal Flash. While this mode provides an excellent environment for silicon evaluation, a stable evaluation environment for testing new algorithms or conducting performance benchmarks, it does have some limitations. Because the monitor/debugger program executes out of the MC9S12DP256's internal memory, the Flash memory, 1024 bytes of the on-chip RAM, and one of the the SCI serial ports are not available to the developer. As shown in Figure 2, D-Bug12 runs on the target system.

# User Terminal RS-232 D-Bug12 Low-Level Interface Routines Target System

Figure 2, EVB Mode Conceptual Model

When operating in the 'EVB' mode, D-Bug12 is not capable of supporting true emulation of a target system. However, programs may be downloaded and executed from the 3072 bytes of the on-chip EEPROM or the portion of on-chip RAM not utilized by D-Bug12. The portion of the RAM that may be used by developer programs begins at \$1000 and ends at \$3BFF. D-Bug12 utilizes the remainder of the RAM which begins at \$3C00 and extends through \$3FFF.

After selecting the EVB operating mode and applying power or pressing the reset button, the sign on message in Figure 3 will be displayed on the screen:

MCS68HC912DP256 EVB

```

D-Bug12 v4.0.0

Copyright 1996 - 2000 Motorola Semiconductor

For Commands type "Help"

```

Figure 3, EVB Mode Sign on Message

D-Bug12 displays the ASCII greater than character (>) indicating that it is ready to accept a command. When issuing a command that causes a program to run from the internal RAM or EEPROM, D-Bug12 will place the terminal cursor on a blank line where it will remain until control is returned to D-Bug12. If a running program fails to return to D-Bug12, pressing the EVB's reset switch will cause the running program to halt execution and initiate the D-Bug12 initialization sequence. Using this method to regain control of an executing program fails to report any information to the programmer on why or how the program may have failed.

Alternately, if an optional S.P.S.T. normally open switch has been wired to the XIRQ interrupt input pin, pressing it generates an XIRQ interrupt causing the running program to halt execution and return control back to D-Bug12 where the CPU register contents are displayed.

# 4.1.1 Interrupts in EVB Mode

D-Bug12 contains default interrupt handlers for all of the implemented MC9S12DP256 interrupt vectors. However, to allow a programmer to utilize peripherals in an interrupt driven manner, a RAM based interrupt vector table is provided by D-Bug12. Each of the 64 entries in the table consists of a two byte address with the table beginning at \$3E00. Initially, all entries in the table have an address of \$0000. Storing a value other than \$0000 in any of the RAM interrupt vector table entries causes execution of the interrupt service routine pointed to by the address when an associated interrupt occurs. The user supplied interrupt service routine must end with an RTI instruction to ensure that execution of the main program continues where it was interrupted.

If an unmasked interrupt occurs and a table entry contains the default address of \$0000, program execution is returned to D-Bug12 where a message is displayed indicating the source of the interrupt and displays the CPU registers at the point where the program was interrupted.

Figure 4 shows the correspondence between the interrupt source and the two byte RAM interrupt vector. Note that even though there is an entry in the table for SCI0, replacing the default value with the address of an interrupt service routine will be ignored since D-Bug12 requires the SCI0 for all of its communication.

| Interrupt Source       | RAM Vector<br>Address | Interrupt Source               | RAM Vector<br>Address |  |

|------------------------|-----------------------|--------------------------------|-----------------------|--|

| Reserved \$FF80        | \$3E00                | IIC Bus                        | \$3E40                |  |

| Reserved \$FF82        | \$3E02                | DLC                            | \$3E42                |  |

| Reserved \$FF84        | \$3E04                | SCME                           | \$3E44                |  |

| Reserved \$FF86        | \$3E06                | CRG Lock                       | \$3E46                |  |

| Reserved \$FF88        | \$3E08                | Pulse Accumulator B Overflow   | \$3E48                |  |

| Reserved \$FF8A        | \$3E0A                | Modulus Down Counter Underflow | \$3E4A                |  |

| PWM Emergency Shutdown | \$3E0C                | Port H Interrupt               | \$3E4C                |  |

| Port P Interrupt       | \$3E0E                | Port J Interrupt               | \$3E4E                |  |

| MSCAN 4 Transmit       | \$3E10                | ATD1                           | \$3E50                |  |

| MSCAN 4 Receive        | \$3E12                | ATD0                           | \$3E52                |  |

| MSCAN 4 Errors         | \$3E14                | SCI1                           | \$3E54                |  |

| MSCAN 4 Wake-up        | \$3E16                | SCI0                           | \$3E56                |  |

| MSCAN 3 Transmit       | \$3E18                | SPI0                           | \$3E58                |  |

| MSCAN 3 Receive        | \$3E1A                | Pulse Accumulator A Input Edge | \$3E5A                |  |

| MSCAN 3 Errors         | \$3E1C                | Pulse Accumulator A Overflow   | \$3E5C                |  |

| MSCAN 3 Wake-up        | \$3E1E                | Timer Overflow                 | \$3E5E                |  |

| MSCAN 2 Transmit       | \$3E20                | Timer Channel 7                | \$3E60                |  |

| MSCAN 2 Receive        | \$3E22                | Timer Channel 6                | \$3E62                |  |

| MSCAN 2 Errors         | \$3E24                | Timer Channel 5                | \$3E64                |  |

| MSCAN 2 Wake-up        | \$3E26                | Timer Channel 4                | \$3E66                |  |

| MSCAN 1 Transmit       | \$3E28                | Timer Channel 3                | \$3E68                |  |

| MSCAN 1 Receive        | \$3E2A                | Timer Channel 2                | \$3E6A                |  |

| MSCAN 1 Errors         | \$3E2C                | Timer Channel 1                | \$3E6C                |  |

| MSCAN 1 Wake-up        | \$3E2E                | Timer Channel 0                | \$3E6E                |  |

| MSCAN 0 Transmit       | \$3E30                | Real Time Interrupt            | \$3E70                |  |

| MSCAN 0 Receive        | \$3E32                | IRQ                            | \$3E72                |  |

| MSCAN 0 Errors         | \$3E34                | XIRQ                           | \$3E74                |  |

| MSCAN 0 Wake-up        | \$3E36                | SWI                            | \$3E76                |  |

| Flash                  | \$3E38                | Unimplemented Instruction Trap | \$3E78                |  |

| EEPROM                 | \$3E3A                | N/A                            | \$3E7A                |  |

| SPI2                   | \$3E3C                | N/A \$3E7C                     |                       |  |

| SPI1                   | \$3E3E                | N/A                            | \$3E7E                |  |

Figure 4, RAM Interrupt Vector Addresses

# 4.1.2 D-Bug12 EVB Mode Memory Map

When D-Bug12 is configured for operation in EVB mode, it runs as a ROM resident monitor. As with all ROM resident monitors, it utilizes some of the on-chip resources to perform its debugging functions. The tables in Figure 5 below detail D-Bug12's memory map when running on the 256K and 128K devices. In both cases, D-Bug12 requires 1024 bytes of the target MCU's on-chip RAM. For the 256K devices, the remaining 11K of RAM may be used for the development of application code. For 128K devices, the remaining 7K of RAM may be used for the development of application code. Note that the current implementation of D-Bug12 does not allow any of the MCU's Flash to be utilized by application code when running in EVB mode.

# MC9S12Dx256

| Address Range   | Description                     |

|-----------------|---------------------------------|

| \$0000 - \$03FF | I/O Registers                   |

| \$0400 - \$0FFF | On-chip EEPROM                  |

| \$1000 - \$3BFF | On-chip RAM (available to user) |

| \$3C00 - \$3FFF | On-chip RAM (D-Bug12)           |

| \$4000 - \$EE7F | D-Bug12 Code                    |

| \$EE80 - \$EEBF | User Accessable Function Table  |

| \$EEC0 - \$EEFF | Customization Data Table        |

| \$EF00 - \$EF8B | D-Bug12 Startup Code            |

| \$EF8C - \$EFFF | Secondary Reset/Interrupt Table |

| \$F000 - \$FFFF | Bootloader                      |

# MC9S12Dx128

| Address Range   | Description                     |

|-----------------|---------------------------------|

| \$0000 - \$03FF | I/O Registers                   |

| \$0800 - \$0FFF | On-chip EEPROM                  |

| \$2000 - \$3BFF | On-chip RAM (available to user) |

| \$3C00 - \$3FFF | On-chip RAM (D-Bug12)           |

| \$4000 - \$EE7F | D-Bug12 Code                    |

| \$EE80 - \$EEBF | User Accessable Function Table  |

| \$EEC0 - \$EEFF | Customization Data Table        |

| \$EF00 - \$EF8B | D-Bug12 Startup Code            |

| \$EF8C - \$EFFF | Secondary Reset/Interrupt Table |

| \$F000 - \$FFFF | Bootloader                      |

|                 |                                 |

Figure 5, D-Bug12 Memory Map In EVB Mode

Note that even though the MC9S12Dx256 parts contain 4K bytes of EEPROM, only the upper 3K bytes are visible as the lower 1K is overlaid by the I/O register block. Also, even though the tables in Figure 5 describe a 64K memory map, the D-Bug12 code occupies on-chip paged Flash memory beginning on page \$38. In addition, most of the lower and upper Fixed Flash pages are utilized by D-Bug12.

# 4.2 POD Mode

In the POD operating mode, none of the MC9S12DP256's resources are available to the developer. Instead, D-Bug12 communicates with the developer's M68HC12 target system through the Single Wire Background Debug interface. This arrangement, as shown in Figure 6, allows access to a developer's target system in a non-intrusive manner. All of the target MCU's resources are available to the developer, providing a non-invasive development environment for the target system.

Figure 6, POD Mode Conceptual Model

On power-up or reset D–Bug12 attempts to establish communications with a target system. Initially, communications is attempted without resetting the target system. This feature allows the POD EVB to be 'hot connected' to a running system without disturbing the target microcontroller. If communications cannot be established, the message shown in Figure 7 is displayed.

```

Can't Communicate With Target CPU

1.) Set Target Speed (8000 KHz)

2.) Reset Target

3.) Reattempt Communication

4.) Erase & Unsecure

5.) Enter BDM debugger

?

```

Figure 7, Failed Target Communications Prompt

Entering the number '1', '2', '3', '4' or '5' from the keyboard allows the developer to configure D–Bug12 for an alternate target frequency, reset the target, attempt to establish communications without resetting the target M68HC12 erase and unsecure an MC9S12 target device or enter the low-level BDM debugger. Entering a character other than the choices provided will result in the target being reset and an attempt to establish communications. The frequency displayed in parenthesis is the current setting for the target crystal frequency.

Entering the number one causes D-Bug12 to make an attempt to measure the target MCU's

operating frequency using the Sync feature of the Enhanced BDM module which is present on most HCS12 family members. If the attempt is successful, communication will be established with the target device resulting in the display of the S> or R> prompt. If the target device does not contain and Enhanced BDM module, the prompt shown in Figure 8 will be displayed.

Enter Target Crystal Frequency (KHz):

Figure 8, Request for Target Frequency Prompt

The entered number must be the target's crystal frequency and **not** the target's E-clock frequency. The entered frequency must be in kilohertz and not hertz. Valid target frequencies range from a low of 32 KHz to a high equal to the crystal frequency of the EVB being used as the POD. Numbers outside this range will result in an error message being displayed and cause the menu of choices to be redisplayed. Each time a valid target crystal frequency is entered, the new value is saved in the EVB's on-chip EEPROM. The saved value is used to initiate communications each time the EVB is powered-up or connected to a new target system.

**Note:** Because of the timing tolerance inherent in the BDM communications protocol and the implementation of the BDM firmware communications primitives, an exact value for the target crystal need not be specified. However, the entered value should be as accurate as possible. For very low frequencies, such as a 32.768 KHz crystal, a value of 32 or 33 will result in proper communication. In reality, the BDM firmware communications primitives will communicate properly with the target microcontroller even if the entered crystal frequency is as much as  $\pm$  20% different from the actual target crystal frequency.

After a valid target crystal frequency has been entered, D–Bug12 will attempt to establish communications with the target processor **without** resetting the target. If the menu of choices is redisplayed, communication could not be established. If communication cannot be established after several attempts, check for the following possible problems:

- The EVB's BDM OUT connector must be properly connected to the target systems BDM connector. If the target system is another MC9S12DP256 EVB, make sure that the POD EVB's BDM OUT connector is connected to the target EVB's BDM IN connector.

- Check for the proper orientation of the BDM cable with the BDM connectors on both the EVB and the target.

- If the target system is not another EVB, verify that its BDM connector is wired to the proper MCU signals on each pin.

- If the target MCU does not have any firmware to execute, the CPU will most likely "run away", possibly executing a STOP instruction, preventing BDM communications with the target MCU. Thus it is strongly recommended that if a target system does not have firmware to execute at power-up or reset, that the target MCU be configured to operate in Special Single Chip mode.

- If the target MCU is a member of the MC9S12 family, has it's security feature enabled and the Flash and EEPROM are not blank, normal BDM communication cannot be

established with the device. Option '4' must first be used to erase the Flash and EEPROM and disable security.

When communications with a target MCU is properly established, either initially or after setting the target crystal frequency, the sign on message in Figure 9 is displayed. Note that this sign on message is identical to that of the sign on message for EVB mode except for the prompt.

```

D-Bug12 v4.0.0

Copyright 1996 - 2000 Motorola Semiconductor

For Commands type "Help"

S>

```

Figure 9, Successful POD Mode Sign on Message

When operating in the POD mode, D-Bug12 will display one of two command prompts depending on the state of the attached target system. When the target system is in active background mode (not running a user program), a two character prompt of 'S>' is displayed. The 'S' in the prompt indicates that the target is Stopped and not running a user program. When the target system is running a user program, a two character prompt of 'R>' is displayed. The 'R' indicates that the target is Running a user program.

Because the M68HC12 Single Wire Background interface allows the reading and writing of target system memory even when the target is running a user's program, the probe microcontroller is always available for the entry of commands. D-Bug12 commands that examine or modify target system memory may be issued when either the 'S>' or 'R>' prompt is displayed.

# 4.2.1 The Erase & Unsecure Option

The security of a microcontroller's program and data memories has long been a concern of companies for one main reason. Because of the considerable time and money that is invested in the development of proprietary algorithms and firmware, it is extremely desirable to keep the firmware and associated data from prying eyes. The MC9S12 (Star12) family members have been designed with a device security mechanism that makes it nearly impossible to access the Flash or EEPROM contents. Once the security mechanism has been enabled, access to the Flash and EEPROM either through the BDM or the expanded bus is inhibited. Gaining access to either of these resources may only be accomplished by erasing the contents of the Flash and EEPROM or through a built in back door mechanism. While having a back door mechanism may seem to be a weakness of the security mechanism, the target application must specifically support this feature for it to operate.

When a secured device is reset in Special Single-chip mode, a special BDM security ROM becomes active. The program in this small ROM performs a blank check of the Flash and EEPROM memories. If both memory spaces are erased, the BDM firmware temporarily disables device security, allowing full BDM functionally. However, if the Flash or EEPROM are not blank, security remains active and only the BDM hardware commands remain functional. In this mode the BDM commands are restricted to reading and writing the I/O register space. Because all other BDM commands and on-chip resources are disabled, the contents of the Flash and EEPROM remain protected. This functionality is adequate to manipulate the Flash and EEPROM control registers to erase their contents.

**Note:** Use of the BDM interface to erase and unsecure the Flash and EEPROM memories is not present in the initial mask set (0K36N) of the MC9S12DP256. Great care must be exercised to ensure that the microcontroller is not programmed in a secure state unless the back door mechanism is supported by the target firmware.

Because normal BDM communication cannot be established with a secured MC9S12 device whose Flash and/or EEPROM are not erased, the Erase and Unsecure option can be used to erase the Flash and EEPROM of a target MC9S12 device and place it in the unsecured state.

# 4.2.2 BDM Debugger Option

The BDM debugger included with D-Bug12 is intended to be used by tool developers or factory engineers when evaluating new silicon or debugging BDM communication problems, however, it may also be useful to end customers. See Appendix D and the documentation associated with the BDMDB command for additioanl information on the BDM debugger.

# 4.3 Jump to EEPROM Mode

This operating mode allows a small program to be executed from the on-chip EEPROM whenever the EVB is powered up or reset. When running on an MC9S12Dx256, MC9S12H256 or MC9S12A256, the bootloader startup code jumps directly to address \$0400 without performing any initialization of the CPU registers or peripherals. When running on a MC9S12Dx128 or MC9S12A128 the EEPROM is not visible at its default address of \$0000 because it is overlayed by the on-chip RAM. In this case, the RAM is relocated to \$2000 and the bootloader startup code jumps directly to address \$0400 without performing any additional initialization of the CPU registers or peripherals.

This mode provides a convenient way to execute a program in a standalone manner without having to erase and program the on-chip Flash using the Bootloader. Code and data can be programmed into the EEPROM using D-Bug12's LOAD command.

**Note:** The MC9S12DP256 contains 4096 bytes of small sector Flash used to 'emulate' EEPROM memory. The default address range of the EEPROM is \$0000 - \$0FFF. Because the default location of the I/O register block occupies the address range from \$0000 - \$03FF, the lower 1024 bytes of the EEPROM is not initially accessible. This is why the 'Jump to EEPROM Mode' jumps to \$0400 instead of the start of the EEPROM. Note that the I/O register block may be relocated by writing to the INITRG register, thus providing access to the lower 1024 bytes of EEPROM memory.

### 4.4 Serial Bootloader Mode

The on-chip Flash memory includes a boot block area from \$F000 - \$FFFF containing an S-Record bootloader program. The bootloader can be used to erase and reprogram the remainder of on-chip Flash memory or erase the on-chip byte erasable EEPROM. The bootloader program utilizes the on-chip SCI for communications and does not require any special programming software on the host computer. The only host software required is a simple terminal program that is capable of communicating at 9600 - 115,200 baud and supports XOn/XOff handshaking.

Invoking the bootloader causes the prompt shown in Figure 10 to be displayed on the host terminal's screen.

HCS912DP256 Bootloader

a) Erase Flash

b) Program Flash

c) Set Baud Rate

d) Erase EEPROM

?

Figure 10, Serial Bootloader Prompt

### 4.4.1 Erase Flash Command

Selecting the Erase function by typing a lower case 'a' on the terminal will cause a bulk erase of all four 64K Flash arrays except for the 4k boot block in the upper 64K array where the S-Record bootloader resides. After the erase operation is completed, a verify operation is performed to ensure that all locations were properly erased. If the erase operation is successful, the bootloader's prompt is redisplayed.

If any locations were found to contain a value other than \$FF, an error message is displayed on the screen and the bootloader's prompt is redisplayed. If the MC9S12DP256 device will not erase after one or two attempts the device may be damaged.

# 4.4.2 Program Flash Command

To increase the efficiency of the programming process, the S-Record bootloader uses interrupt driven, buffered serial I/O in conjunction with XOn/XOff software handshaking to control the flow of S-Record data from the host computer. This allows the bootloader to continue receiving S-Record data from the host computer while the data from the previously received S-Record is programmed into the Flash. The terminal program **must** support XOn/XOff handshaking to properly reprogram the MC9S12DP256's Flash memory.

Typing a lower case 'b' on the terminal causes the bootloader to enter the programming mode and wait for S-Records to be sent from the host computer. The bootloader will continue to receive and process S-Records until it receives an 'S8 or 'S9' end of file record. If the object file being sent to the bootloader does not contain an 'S8' or 'S9' record, the bootloader will not return its prompt and will continue to wait for the end of file record. Pressing the EVB's reset switch, will cause the bootloader to return to its prompt.

If a Flash memory location will not program properly, an error message is displayed on the terminal screen and the bootloader's prompt is redisplayed. If the MC9S12DP256 device will not program after one or two attempts the device may be damaged or an S-Record with a load address outside the range of the available on-chip Flash may have been received. The S-Record data must have load addresses in the range \$C0000 - \$FFFFF. This address range represents the upper 256K bytes of the 1MB address space of the MC9S12DP256.

# 4.4.3 Set Baud Rate Command

While the default communications rate of the bootloader is 9600 baud, this speed is much too slow if the majority of the MC9S12DP256's Flash is to be programmed, however, it provides the best compatibility for initial communications with most terminal programs. The Set Baud Rate command allows the bootloader communication rate to be set to one of four standard baud rates. Using a baud rate of 57,600 allows the entire 256K of flash to be programmed in just under two minutes.

Typing a lower case 'c' on the terminal causes the prompt shown in Figure 11 to be displayed on the host terminal's screen. Entering a number '1' through '4' on the keyboard will select the associated baud rate and issue a secondary prompt indicating that the terminal baud rate should be changed. After changing the terminal baud rate, pressing the enter or return key will return to the main bootloader prompt.

```

1) 9600

2) 38400

3) 57600

4) 115200

? 3

Change Terminal BR, Press Return

```

Figure 11, Change Baud Rate Prompt

# 4.4.4 Reloading D-Bug12

When features or enhancements are added to D-Bug12 it may be desirable to update to the latest version. A .zip distribution file containing the current version of D-Bug12, including the bootloader and Reference Manual, can be obtained electronically from Motorola's web site. Searching the web site for the string "D-Bug12" will return numerous references to D-Bug12. Choosing one of the Product Summary Pages, the distribution file can be found under the "Software/Application Software/dBug ROM Monitors" category.

# 4.4.5 Loading User programs into Flash

While the MC9S12DP256 EVB was designed to be used with the D-Bug12 software to evaluate the MC9S12DP256 device, the board may also be used with user supplied software and hardware to prototype an embedded application. When using the board in this manner the user supplied code may occupy all of the on-chip Flash memory except the address range from \$F000 - \$FFFF in the fixed Flash memory page that begins at \$C000. To begin execution of the users application program, PAD0 and PAD8 must both have jumpers placed in the '0' or 'OFF' position. This will cause the bootloader startup code to jump to the address in the alternate reset vector at \$EFFE. When the user code is programmed into Flash, an address **MUST** be placed in the Reset vector position (\$EFFE) of the alternate interrupt vector table.

# 4.4.6 Erasing the On-chip EEPROM

When D-Bug12 operates in POD mode, it saves various operating parameters and data in the MC9S12DP256's on-chip EEPROM. One of the parameters is the default baud rate. If communication cannot be established with the EVB and random characters are displayed on the terminal screen, it is possible that the baud rate was changed to something other than the current

| sattings of the terminal pro-                                                                 | grom. If attempting                     | . communications         | et verious | hand rates | door not  |

|-----------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------|------------|------------|-----------|

| settings of the terminal pro-<br>result in D-Bug12's prompt<br>reconfigure the baud rate to t | being displayed, the factory default of | ne EVB's on-chip f 9600. | EEPROM     | should be  | erased to |

|                                                                                               |                                         |                          |            |            |           |

|                                                                                               |                                         |                          |            |            |           |

|                                                                                               |                                         |                          |            |            |           |

|                                                                                               |                                         |                          |            |            |           |

|                                                                                               |                                         |                          |            |            |           |

|                                                                                               |                                         |                          |            |            |           |

|                                                                                               |                                         |                          |            |            |           |

|                                                                                               |                                         |                          |            |            |           |

|                                                                                               |                                         |                          |            |            |           |

|                                                                                               |                                         |                          |            |            |           |

|                                                                                               |                                         |                          |            |            |           |

|                                                                                               |                                         |                          |            |            |           |

|                                                                                               |                                         |                          |            |            |           |

|                                                                                               |                                         |                          |            |            |           |

|                                                                                               |                                         |                          |            |            |           |

# 5.0 D-Bug12 Command Summary

The following list summarizes the D-Bug12 command set. Each command's function and command line syntax are described in detail.

- ALTCLK Specify an alternate BDM communications rate.

- ASM Single line assembler/disassembler.

- BAUD Set the SCI communications BAUD rate.

- BDMDB Enter the BDM command debugger.

- BF Block Fill user memory with data.

- BR Set/Display user breakpoints.

- BULK Bulk erase on-chip EEPROM

- CALL Execute a user subroutine, return to D-Bug12 when finished.

- DEVICE Select/define a new target MCU device.

- EEBASE Inform D-Bug12 of the target's EEPROM base address

- FBULK Erase the target processor's on-chip Flash EEPROM

- FLOAD Program the target processor's on-chip Flash EEPROM from S-Records

- FSERASE Erase one or more sectors of target Flash

- G Go. Begin execution of user program.

- GT Go Till. Set a temporary breakpoint and begin execution of user program.

- HELP Display D-Bug12 command set and command syntax.

- LOAD Load user program in S-Record format.

- MD Memory Display. Display memory contents in hex bytes/ASCII format.

- MDW Memory Display Words. Display memory contents in hex words/ASCII format

- MM Memory Modify. Interactively examine/change memory contents.

- MMW Memory Modify Words. Interactively examine/change memory contents.

- MOVE Move a block of memory.

- NOBR Remove one/all user breakpoints.

- PCALL Execute a user subroutine in expanded memory, return to D-Bug12 when finished.

- RD Register Display. Display the CPU register contents.

- REGBASE Inform D-Bug12 of the target's I/O register's base address

- RESET Reset the target CPU

- RM Register Modify. Interactively examine/change CPU register contents.

- SO Step over subroutine calls.

- STOP Stop the execution of user code in the target processor and place the target processor in background mode.

- T Trace. Execute an instruction, disassemble it, and display the CPU registers.

- TCONFIG Configure target before erasing or programming target Flash

- UPLOAD Display memory contents in S-Record format.

- USEHBR Use EVB/Target Hardware breakpoints.

- VER Display the running version of D-Bug12

- VERF Verify memory contents against S-Record Data.

- <RegisterName> <RegisterValue> Set CPU <RegisterName> to <RegisterValue>

# **ALTCLK - Specify An Alternate BDM Communications Rate**

# **Command Line Format**

ALTCLK [<AltBDMRate>]

# **Parameter Description**

<AltBDMRate> - A 16-bit decimal number

# **Command Description**

An errata was introduced in the BDM module on the MC9S12DP256 (Barracuda II) 0K79X mask set and the MC9S12H256 (Mako) 0K78X mask set. When using EXTAL ÷ 2 as the BDM clock source (default) and the PLL is selected as the bus clock source, BDM communications will be lost when the PLL multiplier is greater than 2 ((synr+1))/(refdv+1)). Once communication is lost, the only way to regain communications is to reset the target MCU.

D-Bug12 version 4.0.0b8 and later has been modified to configure the BDM to use the target bus clock (BDM Status Register CLKSW=1) if either of these parts is connected as the target device. Because the BDM interface is being driven by the target bus clock, BDM communication will be lost if the target firmware changes the bus clock frequency using the PLL. To prevent the loss of communications from disrupting a debug session, a command has been added to D-Bug12 that allows an alternate BDM communication clock frequency to be specified. If BDM communication with the target is lost, D-Bug12 will automatically attempt communication at the alternate frequency without notifying the user.

The ALTCLK command is used to specify the alternate BDM communication frequency, which should be equal to the target bus frequency with the PLL engaged as the bus clock. For example, if a 4 MHz crystal/oscillator is being used in a target application and the firmware programs the PLL to generate a 24 MHz bus clock, the ALTCLK command should be used to specify an alternate bus frequency of 24000 KHz. The ALTCLK command must be used to specify the alternate BDM communication frequency **before** executing the target code that engages the PLL as the bus clock. Note that the alternate BDM communication rate specified using the ALTCLK command is saved in D-Bug12's host MCU EEPROM so that it does not have to be reentered each time the development tool is powered up.

Entering the ALTCLK command without an alternate BDM communications frequency will display the current alternate clock setting.

### Restrictions

Switching between the two BDM communications rates is completely transparent to the developer with one exception. If D-Bug12's memory modify command (MM) is used to engage the PLL as the bus clock by setting the PLLSEL bit in the CLKSEL register, D-Bug12 will report that the target memory could not be modified because of the temporary loss of communications. However, after displaying the error message, D-Bug12 will resynchronize to the new BDM communications rate and show that the target memory was properly modified.

The ALTCLK command can only be used if the MC9S12DP256 (Barracuda II) 0K79X mask set or the MC9S12H256 (Mako) 0K78X mask set device is connected as the target device.

# Example

S>ALTCLK 24000

S>ALTCLK

Alternate BDM Clock Frequency (KHz): 24000

S>

# ASM - Single Line Assembler/Disassembler Command

# **Command Line Format**

ASM <Address> | <PPAGENum>:<PPAGEWinAddr>

# **Parameter Description**

<Address> - A 16-bit hexadecimal number or simple expression <PPAGENum> - An 8-bit hexadecimal number or simple expression <PPAGEWinAddr> - A 16-bit hexadecimal number or simple expression

# **Command Description**

The assembler/disassembler is an interactive memory editor that allows memory contents to be viewed and altered using assembly language mnemonics. Each entered source line is translated into machine language code and placed into memory at the time of entry. When displaying memory contents, each instruction is disassembled into its source mnemonic form and displayed along with the hexadecimal machine code and any instruction operands.

Assembler mnemonics and operands may be entered in any mix of upper and lower case letters. Any number of spaces may appear between the assembler prompt and the instruction mnemonic or between the instruction mnemonic and the operand. By default, numeric values appearing in the operand field are interpreted as *signed* decimal numbers. Placing a \$ in front of a number will cause the number to be interpreted as a hexadecimal number.

When an instruction has been disassembled and displayed, the D-Bug12 prompt is displayed following the disassembled instruction. If a carriage return is entered immediately following the prompt, the next instruction in memory is disassembled and displayed on the next line.

If a CPU12 instruction is entered following the prompt, the entered instruction is assembled and placed in memory. The line containing the new entry is erased and the new instruction is disassembled and displayed on the same line. The contents of the next memory location(s) is disassembled and displayed on the screen.

The instruction mnemonics and operand formats accepted by the assembler follow the syntax as described in the M68HC12 Family CPU12 Reference Manual.

There are a number of M68HC11 instruction mnemonics that appear in the M68HC12 Family CPU12 Reference Manual that do not have direct equivalent CPU12 instructions. These mnemonics, listed in the table below, are translated into functionally equivalent CPU12 instructions. To aid the current M68HC11 users that may desire continue to use the M68HC11 mnemonics, the disassembler portion of the assembler/disassembler recognizes the functionally equivalent CPU12 instructions and disassembles those instructions into the equivalent M68HC11 mnemonics.

When entering branch instructions, the number placed in the operand field should be the absolute destination address of the instruction. The assembler will calculate the twos compliment offset of the branch.

The assembly/disassembly process may be terminated by entering a period (.) following the assembler prompt.

# **Restrictions**

None.

| M68HC11 Mnemonic | CPU12 Instruction | M68HC11 Mnemonic                    | CPU12 Instruction                   |

|------------------|-------------------|-------------------------------------|-------------------------------------|

| CLC              | ANDCC #\$FE       | INS                                 | LEAS 1,S                            |

| CLI              | ANDCC #\$EF       | TAP                                 | TFR A,CC                            |

| CLV              | ANDCC #\$FD       | TPA                                 | TFR CC,A                            |

| SEC              | ORCC #\$01        | TSX                                 | TFR S,X                             |

| SEI              | ORCC #\$10        | TSY                                 | TFR S,Y                             |

| SEV              | ORCC #\$02        | XGDX                                | EXG D,X                             |

| ABX              | LEAX B,X          | XGDY                                | EXG D,Y                             |

| ABY              | LEAY B,Y          | SEX R <sub>8</sub> ,R <sub>16</sub> | TFR R <sub>8</sub> ,R <sub>16</sub> |

| DES              | LEAS -1,S         |                                     |                                     |

# M68HC11 to CPU12 Instruction Translation

# Example

><u>ASM 700</u>

0700 CC1000 LDD #4096 0703 1803123401FE MOVW #\$1234,\$01FE 0709 0EF9800001F1 BRSET \$003F,PCR,#\$01,\$0700 070F 18FF TRAP \$FF 0711 183FE3 ETBL <Illegal Addr Mode> >.

# **Assembly Operand Format**

This section describes the operand format used by the assembler when assembling CPU12 instructions. The operand format accepted by the assembler is described separately in the *CPU12 Reference Manual*. Rather that describe the numeric format accepted for each instruction, some general rules will be used. Exceptions and complicated operand formats are described separately.

In general, anywhere the assembler expects a numeric value in the operand field, either a decimal or hexadecimal value may be entered. Decimal numbers are entered as signed constants having a range of -32768..65535. A leading minus sign (-) indicates negative numbers, the absence of a leading minus sign indicates a positive number. A leading plus sign (+) is not allowed. Hexadecimal numbers must be entered with a leading dollar sign (\$) followed by one to four hexadecimal digits. The default number base is decimal.

For all branching instructions, (Bcc, LBcc, BRSET, BRCLR, DBEQ, DBNE, IBEQ, IBNE, TBEQ, TBNE) the number entered in the address portion of the operand field must be the *absolute address of the branch destination*. The assembler will calculate the two's compliment offset to be placed in the assembled object code.

The D–Bug12 assembler allows an optional # symbol to precede the 8-bit mask value in all bit manipulation instructions (BSET, BCLR, BRSET, BRCLR).

# **Disassembly Operand Format**

This section describes the operand format for the disassembler that is used in conjunction with the single line assembler. The operand format used by the disassembler is described separately in the *CPU12 Reference Manual*. Rather that describe the numeric format used for each instruction, some general rules will be applied. Exceptions and complicated operand formats will be described separately.

All numeric values disassembled as hexadecimal numbers will be preceded by a dollar sign (\$) to avoid being confused with values disassembled as signed decimal numbers.

For all branch (Bcc, LBcc, BRSET, BRCLR, DBEQ, DBNE, IBEQ, IBNE, TBEQ, TBNE) instructions the numeric value of the address portion of the operand field will be displayed as the hexadecimal *absolute address of the branch destination*.

All offsets used with indexed addressing modes will be disassembled as *signed* decimal numbers with the following exception. When an instruction is disassembled utilizing the program counter as an index register, the offset field will contain an *absolute hexadecimal address* rather than a decimal offset. The address is calculated by adding the offset in the object code to the value of the program counter at the end of the instruction. Rather than displaying the index register name as 'PC' the mnemonic 'PCR' is used to indicate that the offset field contains an absolute address.

All addresses, whether direct or extended, will be disassembled as four digit hexadecimal numbers.

All 8-bit mask values (BRSET/BRCLR/ANDCC/ORCC) will be disassembled as two digit hexadecimal numbers.

For bit manipulation instructions (BSET, BCLR, BRSET, BRCLR), the disassembler always displays the # symbol preceding the 8-bit mask value.

All 8-bit immediate values will be disassembled as hexadecimal numbers.

All 16-bit immediate values will be disassembled as hexadecimal numbers.

# **BAUD - Change The Communications BAUD Rate**

# **Command Line Format**

```

BAUD <BAUDRate>[;t]

```

# **Parameter Description**

```

<BAUDRate> An unsigned 32-bit decimal number

;t The ASCII string '; t' or '; T'

```

# **Command Description**

The BAUD command is used to change the communications rate of the SCI that is used by D-Bug12 to communicate with the user.

Normally, the newly specified baud rate is saved in non-volitle memory so that it is used the next time the hardware running D-Bug12 is powered up or reset. The ; t command line option may be used to make the baud rate change temporary. The next time the hardware is powered up or reset D-Bug12 will revert to the previously saved baud rate.

# **Restrictions**

Because the <BAUDRate> parameter supplied on the command line is a 32-bit unsigned integer, BAUD rates greater than 65535 baud may be set using this command. The SCI BAUD rate divider value for the requested BAUD rate is calculated using the bus clock value that is supplied in the *CustomizationData* area. Because the SCI BAUD rate divider is a 13-bit counter, certain BAUD rates may not be supported at particular MCU clock frequencies.

# Example

>baud 50

```

Invalid BAUD Rate > baud 115200 Change Terminal BR, Press Return >

```

# **BDMDB** - Enter BDM Debugger

# **Command Line Format**

**BDMDB**

# **Parameter Description**

None.

# **Command Description**

The BDMDB command halts normal D-Bug12 operation and enters the BDM debugger. Using D-Bug12's low level BDM driver routines, the BDM debugger allows individual BDM commands to be sent to a target device directly from the command line. As shown in the example, upon entering the BDM debugger, the command line prompt changes to a question mark (?). Note that while running the BDM debugger, no target BDM communication occurs other than during the execution of a command. Unlike D-Bug12, when running the BDM debugger, no checks are performed to ensure a valid target connection with a target MCU exists before executing a command.

See Appendix D for a complete description of the BDM debugger commands.

# **Restrictions**

The BDMDB command cannot be used when operating in the 'EVB' mode. If the BDMDB command is entered while in 'EVB' mode, an error message will be displayed and command execution will be terminated.

# Example

```

>bdmdb

BDM Command Debugger

For Commands type "HELP"

```

# BF - Fill memory with data

# **Command Line Format**

```

BF <StartAddress> <EndAddress> [<Data>] [;nv]

```

# **Parameter Description**

<StartAddress> A 16-bit hexadecimal number or simple expression <EndAddress> A 16-bit hexadecimal number or simple expression

<Data> An 8-bit hexadecimal number ;nv The ASCII string ';nv' or ';NV'

# **Command Description**

The Block Fill command is used to place a single 8-bit value into a range of memory locations. <StartAddress> is the first memory location written with data and <EndAddress> is the last memory location written with data. If the <data> parameter is omitted the memory range is filled with the value \$00.

Normally the Block Fill command verifies each memory location as it is written. The ';nv' option prevents the Block Fill command from verifying writes to the specified memory range. This option can be useful for testing a range of memory, especially RAM or EEPROM, for defective locations.

# **Restrictions**

None.

# **Example**

```

><u>bf 400 fff 0</u>

><u>bf x x+$ff 55</u>

```

# **BR** - Set/Display User Breakpoints

# **Command Line Format**

BR [<Address> | <PPAGENum>:<PPAGEWinAddr>...]

# **Parameter Description**

<Address>A 16-bit hexadecimal number or simple expression <PPAGENum> - An 8-bit hexadecimal number or simple expression <PPAGEWinAddr> - A 16-bit hexadecimal number or simple expression

# **Command Description**

The BR command is used to set a breakpoint at a specified address or to display any previously set breakpoints. The function of a breakpoint is to halt user program execution when the program reaches the breakpoint address. When a breakpoint address is encountered, D-Bug12 will disassemble the instruction at the breakpoint address, print the CPU12's register contents, and wait for the next D-Bug12 command to be entered by the user.

Breakpoints are set by entering the breakpoint command followed by one or more breakpoint addresses. Entering the breakpoint command without any breakpoint addresses will display all the currently set breakpoints.

A maximum of 10 breakpoints may be set at one time when using software breakpoints (default). A maximum of 2 breakpoints may be set when using the EVB or target CPU's hardware breakpoint capability. For additional information on D-Bug12's hardware breakpoint support, see the USEHBR command description.

### Restrictions

D-Bug12 implements the software breakpoint function by replacing the opcode at the breakpoint address with an SWI instruction when operating in the EVB mode or the BGND instruction when operating in the POD mode. A breakpoint may not be set on a user SWI instruction when operating in EVB mode. In either mode breakpoints may only be set at an opcode address and breakpoints may only be placed at memory addresses implemented as RAM.

When using the on-chip hardware breakpoints, D–Bug12 utilizes the the breakpoint module in either SWI Dual Address (EVB) or BDM Dual Address (POD) mode. Both of these breakpoint module modes utilize the CPU12 instruction fetch tagging mechanism which only allows breakpoints to be set on instruction opcodes.

When operating in the POD mode, new breakpoints may not be set with the BR command when the 'R>' prompt is being displayed. However, the BR command may be used to display breakpoints that are currently set in the user's running program.

# Example

>br 35ec 2f80 c592

Breakpoints: 35ec 2f80 c592

><u>br</u> Breakpoints: 35EC 2F80 C592

# BS - Block Search, Search an Address Range For A Data Pattern

# **Command Line Format**

BS <StartAddress> <EndAddress> '<ASCIIString>' | <Data8> [<Data8>]

# **Parameter Description**

<StartAddress> A 16-bit hexadecimal number or simple expression OR an expanded

memory address

<EndAddress> A 16-bit hexadecimal number or simple expression OR an expanded

memory address

<a href="#"><ASCIIString</a> An ASCII string consisting of any printable characters EXCEPT the single

quote (') character

<Data8> An 8-bit hexadecimal number or simple expression

# **Command Description**

The block search command can be used to search an address range for a data pattern. The specified data can be supplied as a quoted ASCII string or up to eight hexadecimal bytes. If the data pattern is found in the specified memory range, the address of the first byte of the data pattern is displayed. Note that when using an ASCII string as the data pattern, only printable ASCII characters excluding the single quote (') character may be used. The search start and end addresses for parts containing less than 64K of memory are specified using a 16-bit hexadecimal number or simple expression and can span the entire 64K memory map.

Start and end addresses for parts containing 64K or more of (Flash) memory within the PPAGE window range (\$8000 - \$BFFF) must be specified as an expanded memory address range. The expanded address format consists of an 8-bit PPAGE number and a 16-bit PPAGE window address separated by the colon character (':'). The general format of an expanded address is:

```

<PPAGENum>:<PPAGEWinAddr>

```

Both the PPAGE number and the PPAGE window address may consist of a simple expression. <PPAGENum> must be in a valid range for the selected device and <PPAGEWinAddr> must be an address in the PPAGE window (\$8000 - \$BFFF).

For example, to search the entire contents of the on-chip Flash memory of the MC68HC912DA128 for the data pattern \$47, \$6f, \$72, \$64, the following command line would be used:

```

bs 00:8000 07:bfff 47 6f 72 64

```

Note that start and end addresses outside the PPAGE window address **may** include the PPAGE window in the search range. For example, using a start address of \$4000 and an end address of \$F000 for a part containing 64K or more of Flash would include a search of the PPAGE window. However, the data in the PPAGE window range would depend on the value in the PPAGE register at the time of the search.

# Restrictions

If the memory range specified by <StartAddress> and <EndAddress> does not contain at least as many bytes as the specified data, the command will be terminated and an appropriate error message displayed.

The <StartAddress> and <EndAddress> must both be the same address type, i.e. both must be a 16-bit address or both must be an expanded address. If the address types are different, the command will be terminated and an appropriate error message displayed.