## 1.1 Introduction

This block guide provide an overview of serial communication interface (SCI) module. The SCI allows asynchronous serial communications with peripheral devices and other CPUs.

## 1.1.1 Glossary

IRQ — Interrupt Request

LSB — Least Significant Bit

MSB — Most Significant Bit

NRZ — Non-Return-to-Zero

RZI — Return-to-Zero-Inverted

RXD — Receive Pin

SCI — Serial Communication Interface

TXD — Transmit Pin

#### 1.1.2 Features

The SCI includes these distinctive features:

- Full-duplex operation

- Standard mark/space non-return-to-zero (NRZ) format

- 13-bit baud rate selection

- Programmable 8-bit or 9-bit data format

- Separately enabled transmitter and receiver

- Programmable transmitter output parity

- Two receiver wake up methods:

- Idle line wake-up

- Address mark wake-up

- Interrupt-driven operation with eight flags:

- Transmitter empty

- Transmission complete

- Receiver full

- Idle receiver input

- Receiver overrun

- Noise error

- Framing error

- Parity error

- Receiver framing error detection

- Hardware parity checking

- 1/16 bit-time noise detection

## 1.1.3 Modes of Operation

The SCI operation is the same independent of device resource mapping and bus interface mode. Different power modes are available to facilitate power saving.

#### 1.1.3.1 Run Mode

Normal mode of operation.

## 1.1.3.2 Wait Mode

SCI operation in wait mode depends on the state of the SCISWAI bit in the SCI control register 1 (SCICR1).

- If SCISWAI is clear, the SCI operates normally when the CPU is in wait mode.

- If SCISWAI is set, SCI clock generation ceases and the SCI module enters a power-conservation state when the CPU is in wait mode. Setting SCISWAI does not affect the state of the receiver enable bit, RE, or the transmitter enable bit, TE.

- If SCISWAI is set, any transmission or reception in progress stops at wait mode entry. The transmission or reception resumes when either an internal or external interrupt brings the CPU out of wait mode. Exiting wait mode by reset aborts any transmission or reception in progress and resets the SCI.

# 1.1.3.3 Stop Mode

The SCI is inactive during stop mode for reduced power consumption. The STOP instruction does not affect the SCI register states, but the SCI module clock will be disabled. The SCI operation resumes from where it left off after an external interrupt brings the CPU out of stop mode. Exiting stop mode by reset aborts any transmission or reception in progress and resets the SCI.

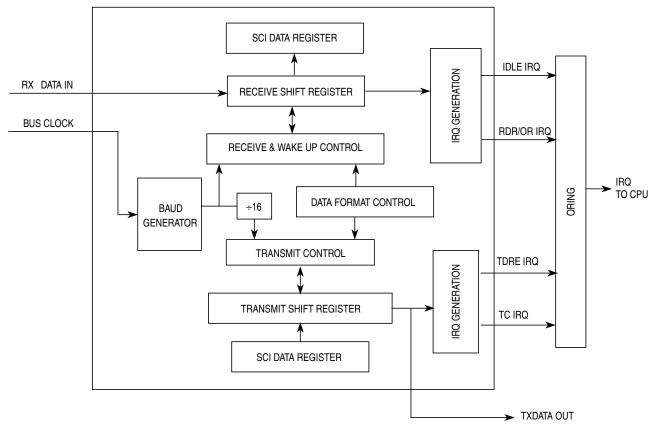

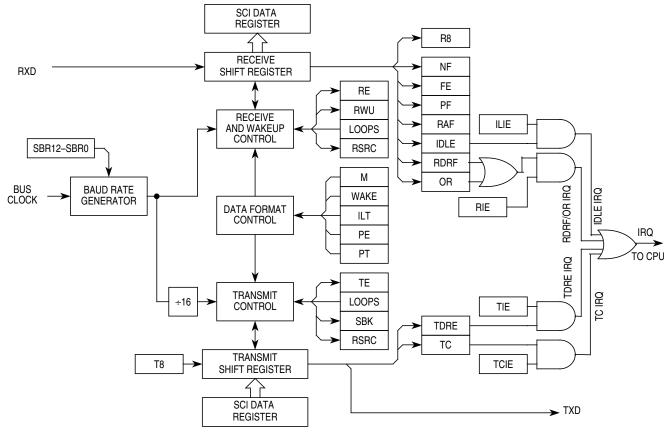

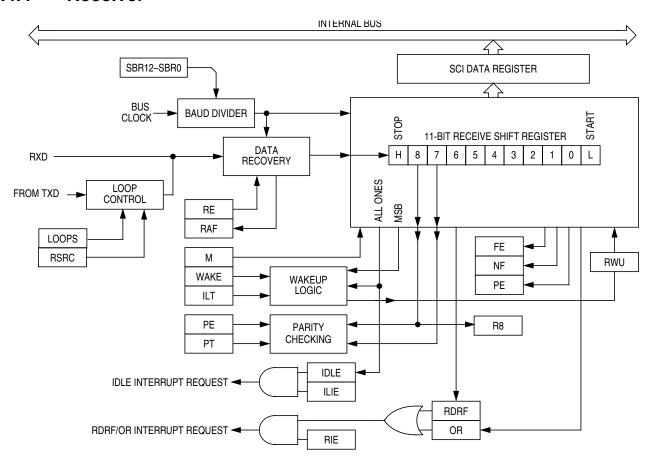

# 1.1.4 Block Diagram

Figure 1-1 is a high level block diagram of the SCI module, showing the interaction of various functional blocks.

Figure 1-1. SCI Block Diagram

# 1.2 External Signal Description

The SCI module has a total of two external pins:

## 1.2.1 TXD-SCI Transmit Pin

This pin serves as transmit data output of SCI.

## 1.2.2 RXD-SCI Receive Pin

This pin serves as receive data input of the SCI.

# 1.3 Memory Map and Registers

This section provides a detailed description of all memory and registers.

## 1.3.1 Module Memory Map

The memory map for the SCI module is given below in Figure 1-2. The Address listed for each register is the address offset. The total address for each register is the sum of the base address for the SCI module and the address offset for each register.

| Address       | Name         |               | Bit 7 | 6          | 5           | 4       | 3      | 2       | 1     | Bit 0 |   |

|---------------|--------------|---------------|-------|------------|-------------|---------|--------|---------|-------|-------|---|

| 0x0000        | SCIBDH       | R             | 0     | 0          | 0           | SBR12   | SBR11  | SBR10   | SBR9  | SBR8  |   |

| ONOGOO        | W            | W             |       |            |             |         | ODITI- | 05.110  |       |       |   |

| 0x0001        | SCIBDL       | R<br>W        | SBR7  | SBR6       | SBR5        | SBR4    | SBR3   | SBR2    | SBR1  | SBR0  |   |

|               |              | R             |       |            |             |         |        |         |       |       |   |

| 0x0002        | SCICR1       | W             | LOOPS | SCISWAI    | RSRC        | М       | WAKE   | ILT     | PE    | PT    |   |

| 0x0003        | SCICR2       | R             | TIE   | TCIE       | RIE         | ILIE    | TE     | RE      | RWU   | SBK   |   |

| CACCCC        | 00.0.42      | W             |       |            |             |         |        |         |       |       |   |

| 0x0004        | SCISR1       | SCISR1 R      | TDRE  | TC         | RDRF        | IDLE    | OR     | NF      | FE    | PF    |   |

| 0,0001        | COIOICI      | W             |       |            |             |         |        |         |       |       |   |

| 0x0005 SCISR2 | SCISR2 R     | R             | 0     | 0          | 0           | 0       | 0      | BRK13   | TXDIR | RAF   |   |

| 0x0003        | 3013112      | W             |       |            |             |         |        | DIXIXIO | INDIK |       |   |

| 0x0006        | ,0006 CCIDDH | 0x0006 SCIDRH | R     | R8         | T8          | 0       | 0      | 0       | 0     | 0     | 0 |

| 000000        | SCIDKIT      | SCIDKH W      |       | 10         |             |         |        |         |       |       |   |

| 0x0007        | SCIDRL       | R             | R7    | R6         | R5          | R4      | R3     | R2      | R1    | R0    |   |

|               | SCIDEL       | W             | T7    | T6         | T5          | T4      | T3     | T2      | T1    | T0    |   |

|               |              | [             |       | = Unimplen | nented or R | eserved |        |         |       |       |   |

Figure 1-2. SCI Register Summary

# 1.3.2 Register Descriptions

This section consists of register descriptions in address order. Each description includes a standard register diagram with an associated figure number. Writes to a reserved register location do not have any effect and reads of these locations return a zero. Details of register bit and field function follow the register diagrams, in bit order.

## 1.3.2.1 SCI Baud Rate Registers (SCIBDH and SCHBDL)

Module Base + 0x\_0000 3 2 1 0 0 R 0 SBR12 SBR11 SBR10 SBR9 SBR8 W 0 0 0 0 0 0 0 0 Reset Module Base + 0x\_0001 7 2 0 6 5 4 3 1 R SBR7 SBR6 SBR5 SBR4 SBR3 SBR2 SBR1 SBR0 W 0 0 0 0 0 1 0 0 Reset

Figure 1-3. SCI Baud Rate Registers (SCIBDH and SCIBDL)

The SCI Baud Rate Register is used by the counter to determine the baud rate of the SCI. The formula for calculating the baud rate is:

SCI baud rate = SCI module clock /  $(16 \times BR)$

= Unimplemented or Reserved

#### where:

BR is the content of the SCI baud rate registers, bits SBR12 through SBR0. The baud rate registers can contain a value from 1 to 8191.

Read: Anytime. If only SCIBDH is written to, a read will not return the correct data until SCIBDL is written to as well, following a write to SCIBDH.

Write: Anytime

Table 1-1. SCIBDH AND SCIBDL Field Descriptions

| Field                   | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4-0<br>7-0<br>SBR[12:0] | SCI Baud Rate Bits — The baud rate for the SCI is determined by these 13 bits.  Note: The baud rate generator is disabled until the TE bit or the RE bit is set for the first time after reset. The baud rate generator is disabled when BR = 0.  Writing to SCIBDH has no effect without writing to SCIBDL, since writing to SCIBDH puts the data in a temporary location until SCIBDL is written to. |

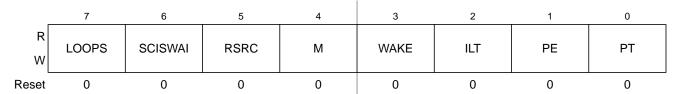

# 1.3.2.2 SCI Control Register 1 (SCICR1)

Module Base + 0x\_0002

Figure 1-4. SCI Control Register 1 (SCICR1)

Read: Anytime Write: Anytime

Table 1-2. SCICR1 Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LOOPS   | Loop Select Bit — LOOPS enables loop operation. In loop operation, the RXD pin is disconnected from the SCI and the transmitter output is internally connected to the receiver input. Both the transmitter and the receiver must be enabled to use the loop function. See Table 1-3.  0 Normal operation enabled 1 Loop operation enabled Note: The receiver input is determined by the RSRC bit.                                                                                                                                                               |

| 6<br>SCISWAI | SCI Stop in Wait Mode Bit — SCISWAI disables the SCI in wait mode.  0 SCI enabled in wait mode  1 SCI disabled in wait mode                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5<br>RSRC    | Receiver Source Bit — When LOOPS = 1, the RSRC bit determines the source for the receiver shift register input.  O Receiver input internally connected to transmitter output  Receiver input connected externally to transmitter                                                                                                                                                                                                                                                                                                                                |

| 4<br>M       | Data Format Mode Bit — MODE determines whether data characters are eight or nine bits long.  One start bit, eight data bits, one stop bit  One start bit, nine data bits, one stop bit                                                                                                                                                                                                                                                                                                                                                                          |

| 3<br>WAKE    | Wakeup Condition Bit — WAKE determines which condition wakes up the SCI: a logic 1 (address mark) in the most significant bit position of a received data character or an idle condition on the RXD.  O Idle line wakeup  1 Address mark wakeup                                                                                                                                                                                                                                                                                                                 |

| 2<br>ILT     | Idle Line Type Bit — ILT determines when the receiver starts counting logic 1s as idle character bits. The counting begins either after the start bit or after the stop bit. If the count begins after the start bit, then a string of logic 1s preceding the stop bit may cause false recognition of an idle character. Beginning the count after the stop bit avoids false idle character recognition, but requires properly synchronized transmissions.  O Idle character bit count begins after start bit  I Idle character bit count begins after stop bit |

| 1<br>PE      | Parity Enable Bit — PE enables the parity function. When enabled, the parity function inserts a parity bit in the most significant bit position.  O Parity function disabled  Parity function enabled                                                                                                                                                                                                                                                                                                                                                           |

| 0<br>PT      | Parity Type Bit — PT determines whether the SCI generates and checks for even parity or odd parity. With even parity, an even number of 1s clears the parity bit and an odd number of 1s sets the parity bit. With odd parity, an odd number of 1s clears the parity bit and an even number of 1s sets the parity bit.  0 Even parity  1 Odd parity                                                                                                                                                                                                             |

**Table 1-3. Loop Functions**

| LOOPS | RSRC | Function                                                  |

|-------|------|-----------------------------------------------------------|

| 0     | х    | Normal operation                                          |

| 1     | 0    | Loop mode with Rx input internally connected to Tx output |

| 1     | 1    | Single-wire mode with Rx input connected to TXD           |

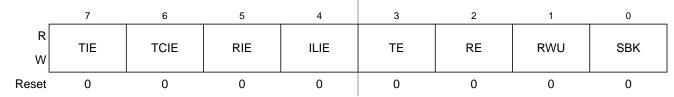

# 1.3.2.3 SCI Control Register 2 (SCICR2)

Module Base + 0x\_0003

Figure 1-5. SCI Control Register 2 (SCICR2)

Read: Anytime Write: Anytime

**Table 1-4. SCICR2 Field Descriptions**

| Field     | Description                                                                                                                                                                                                                               |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TIE  | Transmitter Interrupt Enable Bit — TIE enables the transmit data register empty flag, TDRE, to generate interrupt requests.  O TDRE interrupt requests disabled  1 TDRE interrupt requests enabled                                        |

| 6<br>TCIE | Transmission Complete Interrupt Enable Bit — TCIE enables the transmission complete flag, TC, to generate interrupt requests.  O TC interrupt requests disabled  1 TC interrupt requests enabled                                          |

| 5<br>RIE  | Receiver Full Interrupt Enable Bit — RIE enables the receive data register full flag, RDRF, or the overrun flag, OR, to generate interrupt requests.  O RDRF and OR interrupt requests disabled  1 RDRF and OR interrupt requests enabled |

| 4<br>ILIE | Idle Line Interrupt Enable Bit — ILIE enables the idle line flag, IDLE, to generate interrupt requests.  0 IDLE interrupt requests disabled 1 IDLE interrupt requests enabled                                                             |

| 3<br>TE   | Transmitter Enable Bit — TE enables the SCI transmitter and configures the TXD pin as being controlled by the SCI. The TE bit can be used to queue an idle preamble.  0 Transmitter disabled 1 Transmitter enabled                        |

| 2<br>RE   | Receiver Enable Bit — RE enables the SCI receiver.  0 Receiver disabled 1 Receiver enabled                                                                                                                                                |

Table 1-4. SCICR2 Field Descriptions (continued)

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>RWU | Receiver Wakeup Bit — Standby state  0 Normal operation.  1 RWU enables the wakeup function and inhibits further receiver interrupt requests. Normally, hardware wakes the receiver by automatically clearing RWU.                                                                                                                                                                                            |

| 0<br>SBK | Send Break Bit — Toggling SBK sends one break character (10 or 11 logic 0s, respectively 13 or 14 logics 0s if BRK13 is set). Toggling implies clearing the SBK bit before the break character has finished transmitting. As long as SBK is set, the transmitter continues to send complete break characters (10 or 11 bits, respectively 13 or 14 bits).  O No break characters  1 Transmit break characters |

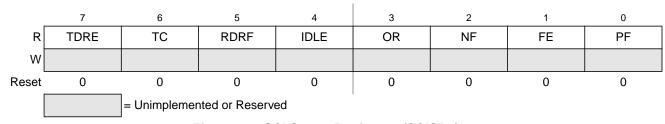

## 1.3.2.4 SCI Status Register 1 (SCISR1)

The SCISR1 and SCISR2 registers provides inputs to the MCU for generation of SCI interrupts. Also, these registers can be polled by the MCU to check the status of these bits. The flag-clearing procedures require that the status register be read followed by a read or write to the SCI Data Register.It is permissible to execute other instructions between the two steps as long as it does not compromise the handling of I/O, but the order of operations is important for flag clearing.

Module Base + 0x\_0004

Figure 1-6. SCI Status Register 1 (SCISR1)

Read: Anytime

Write: Has no meaning or effect

Table 1-5. SCISR1 Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TDRE | Transmit Data Register Empty Flag — TDRE is set when the transmit shift register receives a byte from the SCI data register. When TDRE is 1, the transmit data register (SCIDRH/L) is empty and can receive a new value to transmit.Clear TDRE by reading SCI status register 1 (SCISR1), with TDRE set and then writing to SCI data register low (SCIDRL).  0 No byte transferred to transmit shift register  1 Byte transferred to transmit shift register; transmit data register empty                                                                                                                                                                                         |

| 6<br>TC   | Transmit Complete Flag — TC is set low when there is a transmission in progress or when a preamble or break character is loaded. TC is set high when the TDRE flag is set and no data, preamble, or break character is being transmitted. When TC is set, the TXD out signal becomes idle (logic 1). Clear TC by reading SCI status register 1 (SCISR1) with TC set and then writing to SCI data register low (SCIDRL). TC is cleared automatically when data, preamble, or break is queued and ready to be sent. TC is cleared in the event of a simultaneous set and clear of the TC flag (transmission not complete).  0 Transmission in progress 1 No transmission in progress |

Table 1-5. SCISR1 Field Descriptions (continued)

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>RDRF | Receive Data Register Full Flag — RDRF is set when the data in the receive shift register transfers to the SCI data register. Clear RDRF by reading SCI status register 1 (SCISR1) with RDRF set and then reading SCI data register low (SCIDRL).  0 Data not available in SCI data register  1 Received data available in SCI data register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4<br>IDLE | Idle Line Flag — IDLE is set when 10 consecutive logic 1s (if M=0) or 11 consecutive logic 1s (if M=1) appear on the receiver input. Once the IDLE flag is cleared, a valid frame must again set the RDRF flag before an idle condition can set the IDLE flag.Clear IDLE by reading SCI status register 1 (SCISR1) with IDLE set and then reading SCI data register low (SCIDRL).  O Receiver input is either active now or has never become active since the IDLE flag was last cleared Receiver input has become idle Note: When the receiver wakeup bit (RWU) is set, an idle line condition does not set the IDLE flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3<br>OR   | Overrun Flag — OR is set when software fails to read the SCI data register before the receive shift register receives the next frame. The OR bit is set immediately after the stop bit has been completely received for the second frame. The data in the shift register is lost, but the data already in the SCI data registers is not affected. Clear OR by reading SCI status register 1 (SCISR1) with OR set and then reading SCI data register low (SCIDRL).  O No overrun  Note: OR flag may read back as set when RDRF flag is clear. This may happen if the following sequence of events occurs:  1. After the first frame is received, read status register SCISR1 (returns RDRF set and OR flag clear); 2. Receive second frame without reading the first frame in the data register (the second frame is not received and OR flag is set); 3. Read data register SCIDRL (returns first frame and clears RDRF flag in the status register); 4. Read status register SCISR1 (returns RDRF clear and OR set).  Event 3 may be at exactly the same time as event 2 or any time after. When this happens, a dummy SCIDRL read following event 4 will be required to clear the OR flag if further frames are to be received. |

| 2<br>NF   | Noise Flag — NF is set when the SCI detects noise on the receiver input. NF bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. Clear NF by reading SCI status register 1(SCISR1), and then reading SCI data register low (SCIDRL).  O No noise Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1<br>FE   | Framing Error Flag — FE is set when a logic 0 is accepted as the stop bit. FE bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. FE inhibits further data reception until it is cleared. Clear FE by reading SCI status register 1 (SCISR1) with FE set and then reading the SCI data register low (SCIDRL).  O No framing error  Traming error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0<br>PF   | Parity Error Flag — PF is set when the parity enable bit (PE) is set and the parity of the received data does not match the parity type bit (PT). PF bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. Clear PF by reading SCI status register 1 (SCISR1), and then reading SCI data register low (SCIDRL).  O No parity error  1 Parity error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

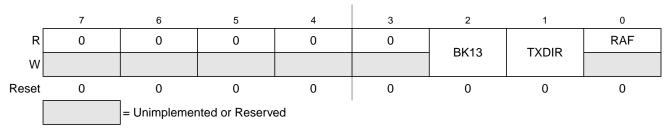

## 1.3.2.5 SCI Status Register 2 (SCISR2)

Module Base + 0x\_0005

Figure 1-7. SCI Status Register 2 (SCISR2)

Read: Anytime

Write: Anytime; writing accesses SCI status register 2; writing to any bits except TXDIR and BRK13 (SCISR2[1] & [2]) has no effect

**Table 1-6. SCISR2 Field Descriptions**

| Field      | Description                                                                                                                                                                                                                                                                                                                                                 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>BK13  | Break Transmit Character Length — This bit determines whether the transmit break character is 10 or 11 bit respectively 13 or 14 bits long. The detection of a framing error is not affected by this bit.  0 Break Character is 10 or 11 bit long  1 Break character is 13 or 14 bit long                                                                   |

| 1<br>TXDIR | Transmitter Pin Data Direction in Single-Wire Mode. — This bit determines whether the TXD pin is going to be used as an input or output, in the Single-Wire mode of operation. This bit is only relevant in the Single-Wire mode of operation.  O TXD pin to be used as an input in Single-Wire mode  1 TXD pin to be used as an output in Single-Wire mode |

| 0<br>RAF   | Receiver Active Flag — RAF is set when the receiver detects a logic 0 during the RT1 time period of the start bit search. RAF is cleared when the receiver detects an idle character.  0 No reception in progress 1 Reception in progress                                                                                                                   |

## 1.3.2.6 SCI Data Registers (SCIDRH and SCIDRL)

Module Base + 0x\_0006 6 R R8 0 0 0 0 0 0 T8 W 0 0 0 0 0 0 0 0 Reset Module Base + 0x\_0007 7 6 5 3 2 0 4 1 R R7 R6 R5 R4 R3 R2 R1 R0 W T7 T1 T6 T5 T4 Т3 T2 T0 0 0 0 0 0 0 0 Reset 0 Unimplemented or Reserved

Figure 1-8. SCI Data Registers (SCIDRH and SCIDRL)

Read: Anytime; reading accesses SCI receive data register

Write: Anytime; writing accesses SCI transmit data register; writing to R8 has no effect

Field

Pescription

Received Bit 8 — R8 is the ninth data bit received when the SCI is configured for 9-bit data format (M = 1).

Transmit Bit 8 — T8 is the ninth data bit transmitted when the SCI is configured for 9-bit data format (M = 1).

Too

Received Bits — Received bits seven through zero for 9-bit or 8-bit data formats

Transmit Bits — Transmit bits seven through zero for 9-bit or 8-bit formats

Table 1-7. SCIDRH AND SCIDRL Field Descriptions

#### **NOTE**

If the value of T8 is the same as in the previous transmission, T8 does not have to be rewritten. The same value is transmitted until T8 is rewritten

In 8-bit data format, only SCI data register low (SCIDRL) needs to be accessed.

When transmitting in 9-bit data format and using 8-bit write instructions, write first to SCI data register high (SCIDRH), then SCIDRL.

# 1.4 Functional Description

This section provides a complete functional description of the SCI block, detailing the operation of the design from the end user perspective in a number of subsections.

Figure 1-9 shows the structure of the SCI module. The SCI allows full duplex, asynchronous, NRZ serial communication between the CPU and remote devices, including other CPUs. The SCI transmitter and receiver operate independently, although they use the same baud rate generator. The CPU monitors the status of the SCI, writes the data to be transmitted, and processes received data.

Figure 1-9. SCI Block Diagram

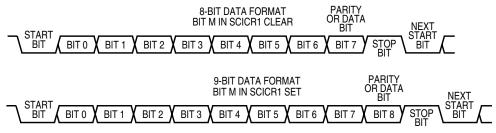

#### 1.4.1 Data Format

The SCI uses the standard NRZ mark/space data format illustrated in Figure 1-10 below.

Figure 1-10. SCI Data Formats

Each data character is contained in a frame that includes a start bit, eight or nine data bits, and a stop bit. Clearing the M bit in SCI control register 1 configures the SCI for 8-bit data characters. A frame with eight data bits has a total of 10 bits. Setting the M bit configures the SCI for nine-bit data characters. A frame with nine data bits has a total of 11 bits

Start Stop Data **Address Parity** Bit **Bits Bits Bits** Bit 1 8 0 0 1 7 1 0 1 1

0

1

Table 1-8. Example of 8-Bit Data Formats

1<sup>1</sup>

1

7

When the SCI is configured for 9-bit data characters, the ninth data bit is the T8 bit in SCI data register high (SCIDRH). It remains unchanged after transmission and can be used repeatedly without rewriting it. A frame with nine data bits has a total of 11 bits.

Table 1-9. Example of 9-Bit Data Formats

| Start<br>Bit | Data<br>Bits | Address<br>Bits | Parity<br>Bits | Stop<br>Bit |

|--------------|--------------|-----------------|----------------|-------------|

| 1            | 9            | 0               | 0              | 1           |

| 1            | 8            | 0               | 1              | 1           |

| 1            | 8            | 1 <sup>1</sup>  | 0              | 1           |

The address bit identifies the frame as an address character. See Section 1.4.4.6, "Receiver Wakeup".

The address bit identifies the frame as an address character. See Section 1.4.4.6, "Receiver Wakeup".

#### 1.4.2 Baud Rate Generation

A 13-bit modulus counter in the baud rate generator derives the baud rate for both the receiver and the transmitter. The value from 0 to 8191 written to the SBR12–SBR0 bits determines the module clock divisor. The SBR bits are in the SCI baud rate registers (SCIBDH and SCIBDL). The baud rate clock is synchronized with the bus clock and drives the receiver. The baud rate clock divided by 16 drives the transmitter. The receiver has an acquisition rate of 16 samples per bit time.

Baud rate generation is subject to one source of error:

Integer division of the module clock may not give the exact target frequency.

Table 1-10 lists some examples of achieving target baud rates with a module clock frequency of 25 MHz SCI baud rate = SCI module clock / (16 \* SCIBR[12:0])

Table 1-10. Baud Rates (Example: Module Clock = 25 MHz)

| Bits<br>SBR[12-0] | Receiver<br>Clock (Hz) | Transmitter<br>Clock (Hz) | Target Baud<br>Rate | Error<br>(%) |

|-------------------|------------------------|---------------------------|---------------------|--------------|

| 41                | 609,756.1              | 38,109.8                  | 38,400              | .76          |

| 81                | 308,642.0              | 19,290.1                  | 19,200              | .47          |

| 163               | 153,374.2              | 9585.9                    | 9600                | .16          |

| 326               | 76,687.1               | 4792.9                    | 4800                | .15          |

| 651               | 38,402.5               | 2400.2                    | 2400                | .01          |

| 1302              | 19,201.2               | 1200.1                    | 1200                | .01          |

| 2604              | 9600.6                 | 600.0                     | 600                 | .00          |

| 5208              | 4800.0                 | 300.0                     | 300                 | .00          |

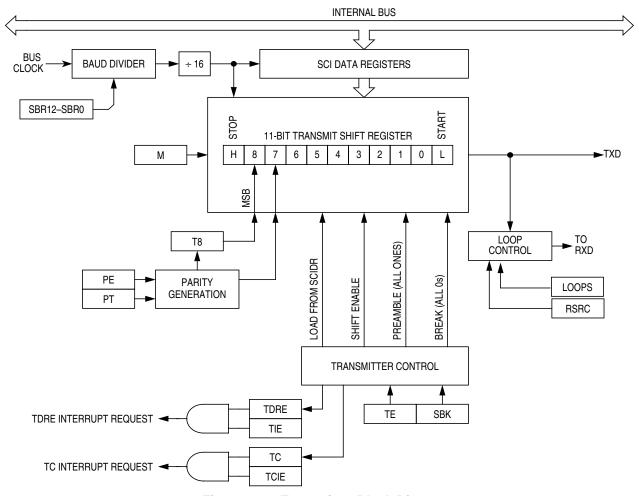

#### 1.4.3 Transmitter

Figure 1-11. Transmitter Block Diagram

## 1.4.3.1 Transmitter Character Length

The SCI transmitter can accommodate either 8-bit or 9-bit data characters. The state of the M bit in SCI control register 1 (SCICR1) determines the length of data characters. When transmitting 9-bit data, bit T8 in SCI data register high (SCIDRH) is the ninth bit (bit 8).

#### 1.4.3.2 Character Transmission

To transmit data, the MCU writes the data bits to the SCI data registers (SCIDRH/SCIDRL), which in turn are transferred to the transmitter shift register. The transmit shift register then shifts a frame out through the **Tx output** signal, after it has prefaced them with a start bit and appended them with a stop bit. The SCI data registers (SCIDRH and SCIDRL) are the write-only buffers between the internal data bus and the transmit shift register.

The SCI also sets a flag, the transmit data register empty flag (TDRE), every time it transfers data from the buffer (SCIDRH/L) to the transmitter shift register. The transmit driver routine may respond to this flag

by writing another byte to the Transmitter buffer (SCIDRH/SCIDRL), while the shift register is still shifting out the first byte.

To initiate an SCI transmission:

- 1. Configure the SCI:

- a) Select a baud rate. Write this value to the SCI baud registers (SCIBDH/L) to begin the baud rate generator. Remember that the baud rate generator is disabled when the baud rate is zero. Writing to the SCIBDH has no effect without also writing to SCIBDL.

- b) Write to SCICR1 to configure word length, parity, and other configuration bits (LOOPS,RSRC,M,WAKE,ILT,PE,PT).

- c) Enable the transmitter, interrupts, receive, and wake up as required, by writing to the SCICR2 register bits (TIE,TCIE,RIE,ILIE,TE,RE,RWU,SBK). A preamble or idle character will now be shifted out of the transmitter shift register.

- 2. Transmit Procedure for Each Byte:

- a. Poll the TDRE flag by reading the SCISR1 or responding to the TDRE interrupt. Keep in mind that the TDRE bit resets to one.

- d) If the TDRE flag is set, write the data to be transmitted to SCIDRH/L, where the ninth bit is written to the T8 bit in SCIDRH if the SCI is in 9-bit data format. A new transmission will not result until the TDRE flag has been cleared.

- 3. Repeat step 2 for each subsequent transmission.

#### NOTE

The TDRE flag is set when the shift register is loaded with the next data to be transmitted from SCIDRH/L, which happens, generally speaking, a little over half-way through the stop bit of the previous frame. Specifically, this transfer occurs 9/16ths of a bit time AFTER the start of the stop bit of the previous frame.

Writing the TE bit from 0 to a 1 automatically loads the transmit shift register with a preamble of 10 logic 1s (if M=0) or 11 logic 1s (if M=1). After the preamble shifts out, control logic transfers the data from the SCI data register into the transmit shift register. A logic 0 start bit automatically goes into the least significant bit position of the transmit shift register. A logic 1 stop bit goes into the most significant bit position.

Hardware supports odd or even parity. When parity is enabled, the most significant bit (msb) of the data character is the parity bit.

The transmit data register empty flag, TDRE, in SCI status register 1 (SCISR1) becomes set when the SCI data register transfers a byte to the transmit shift register. The TDRE flag indicates that the SCI data register can accept new data from the internal data bus. If the transmit interrupt enable bit, TIE, in SCI control register 2 (SCICR2) is also set, the TDRE flag generates a transmitter interrupt request.

When the transmit shift register is not transmitting a frame, the **Tx output** signal goes to the idle condition, logic 1. If at any time software clears the TE bit in SCI control register 2 (SCICR2), the transmitter enable signal goes low and the transmit signal goes idle.

If software clears TE while a transmission is in progress (TC = 0), the frame in the transmit shift register continues to shift out. To avoid accidentally cutting off the last frame in a message, always wait for TDRE to go high after the last frame before clearing TE.

To separate messages with preambles with minimum idle line time, use this sequence between messages:

- 1. Write the last byte of the first message to SCIDRH/L.

- 2. Wait for the TDRE flag to go high, indicating the transfer of the last frame to the transmit shift register.

- 3. Queue a preamble by clearing and then setting the TE bit.

- 4. Write the first byte of the second message to SCIDRH/L.

#### 1.4.3.3 Break Characters

Writing a logic 1 to the send break bit, SBK, in SCI control register 2 (SCICR2) loads the transmit shift register with a break character. A break character contains all logic 0s and has no start, stop, or parity bit. Break character length depends on the M bit in SCI control register 1 (SCICR1). As long as SBK is at logic 1, transmitter logic continuously loads break characters into the transmit shift register. After software clears the SBK bit, the shift register finishes transmitting the last break character and then transmits at least one logic 1. The automatic logic 1 at the end of a break character guarantees the recognition of the start bit of the next frame.

The SCI recognizes a break character when a start bit is followed by eight or nine logic 0 data bits and a logic 0 where the stop bit should be. Receiving a break character has these effects on SCI registers:

- Sets the framing error flag, FE

- Sets the receive data register full flag, RDRF

- Clears the SCI data registers (SCIDRH/L)

- May set the overrun flag, OR, noise flag, NF, parity error flag, PE, or the receiver active flag, RAF (see Section 1.3.2.4, "SCI Status Register 1 (SCISR1)" and Section 1.3.2.5, "SCI Status Register 2 (SCISR2)"

#### 1.4.3.4 Idle Characters

An idle character contains all logic 1s and has no start, stop, or parity bit. Idle character length depends on the M bit in SCI control register 1 (SCICR1). The preamble is a synchronizing idle character that begins the first transmission initiated after writing the TE bit from 0 to 1.

If the TE bit is cleared during a transmission, the **Tx output** signal becomes idle after completion of the transmission in progress. Clearing and then setting the TE bit during a transmission queues an idle character to be sent after the frame currently being transmitted.

#### **NOTE**

When queueing an idle character, return the TE bit to logic 1 before the stop bit of the current frame shifts out through the **Tx output** signal. Setting TE after the stop bit appears on **Tx output signal** causes data previously written to the SCI data register to be lost. Toggle the TE bit for a queued idle character while the TDRE flag is set and immediately before writing the next byte to the SCI data register.

#### **NOTE**

If the TE bit is clear and the transmission is complete, the SCI is not the master of the TXD pin

#### 1.4.4 Receiver

Figure 1-12. SCI Receiver Block Diagram

## 1.4.4.1 Receiver Character Length

The SCI receiver can accommodate either 8-bit or 9-bit data characters. The state of the M bit in SCI control register 1 (SCICR1) determines the length of data characters. When receiving 9-bit data, bit R8 in SCI data register high (SCIDRH) is the ninth bit (bit 8).

## 1.4.4.2 Character Reception

During an SCI reception, the receive shift register shifts a frame in from the **Rx input** signal. The SCI data register is the read-only buffer between the internal data bus and the receive shift register.

After a complete frame shifts into the receive shift register, the data portion of the frame transfers to the SCI data register. The receive data register full flag, RDRF, in SCI status register 1 (SCISR1) becomes set, indicating that the received byte can be read. If the receive interrupt enable bit, RIE, in SCI control register 2 (SCICR2) is also set, the RDRF flag generates an RDRF interrupt request.

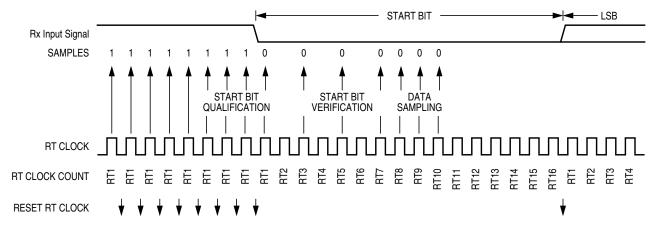

## 1.4.4.3 Data Sampling

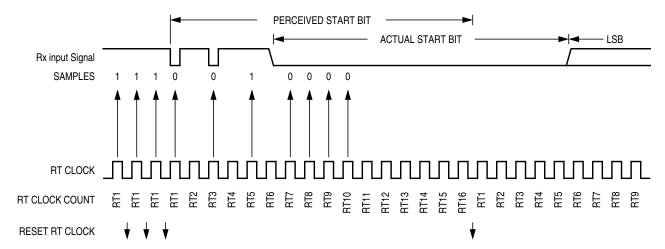

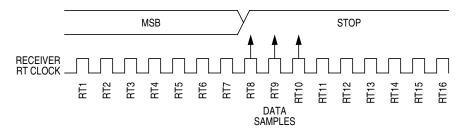

The receiver samples the **Rx input** signal at the RT clock rate. The RT clock is an internal signal with a frequency 16 times the baud rate. To adjust for baud rate mismatch, the RT clock (see Figure 1-13) is re-synchronized:

- After every start bit

- After the receiver detects a data bit change from logic 1 to logic 0 (after the majority of data bit samples at RT8, RT9, and RT10 returns a valid logic 1 and the majority of the next RT8, RT9, and RT10 samples returns a valid logic 0)

To locate the start bit, data recovery logic does an asynchronous search for a logic 0 preceded by three logic 1s. When the falling edge of a possible start bit occurs, the RT clock begins to count to 16.

Figure 1-13. Receiver Data Sampling

To verify the start bit and to detect noise, data recovery logic takes samples at RT3, RT5, and RT7. Table 1-11 summarizes the results of the start bit verification samples.

| RT3, RT5, and RT7 Samples | Start Bit Verification | Noise Flag |

|---------------------------|------------------------|------------|

| 000                       | Yes                    | 0          |

| 001                       | Yes                    | 1          |

| 010                       | Yes                    | 1          |

| 011                       | No                     | 0          |

Table 1-11. Start Bit Verification

Table 1-11. Start Bit Verification

| RT3, RT5, and RT7 Samples | Start Bit Verification | Noise Flag |

|---------------------------|------------------------|------------|

| 100                       | Yes                    | 1          |

| 101                       | No                     | 0          |

| 110                       | No                     | 0          |

| 111                       | No                     | 0          |

If start bit verification is not successful, the RT clock is reset and a new search for a start bit begins.

To determine the value of a data bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 1-12 summarizes the results of the data bit samples.

Table 1-12. Data Bit Recovery

| RT8, RT9, and RT10 Samples | Data Bit Determination | Noise Flag |

|----------------------------|------------------------|------------|

| 000                        | 0                      | 0          |

| 001                        | 0                      | 1          |

| 010                        | 0                      | 1          |

| 011                        | 1                      | 1          |

| 100                        | 0                      | 1          |

| 101                        | 1                      | 1          |

| 110                        | 1                      | 1          |

| 111                        | 1                      | 0          |

#### **NOTE**

The RT8, RT9, and RT10 samples do not affect start bit verification. If any or all of the RT8, RT9, and RT10 start bit samples are logic 1s following a successful start bit verification, the noise flag (NF) is set and the receiver assumes that the bit is a start bit (logic 0).

To verify a stop bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 1-13 summarizes the results of the stop bit samples.

Table 1-13. Stop Bit Recovery

| RT8, RT9, and RT10 Samples | Framing Error Flag | Noise Flag |

|----------------------------|--------------------|------------|

| 000                        | 1                  | 0          |

| 001                        | 1                  | 1          |

| 010                        | 1                  | 1          |

| 011                        | 0                  | 1          |

| 100                        | 1                  | 1          |

| 101                        | 0                  | 1          |

| 110                        | 0                  | 1          |

| 111                        | 0                  | 0          |

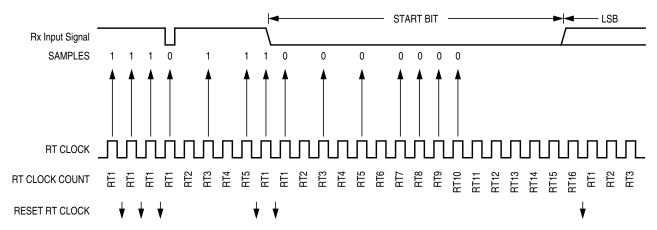

In Figure 1-14 the verification samples RT3 and RT5 determine that the first low detected was noise and not the beginning of a start bit. The RT clock is reset and the start bit search begins again. The noise flag is not set because the noise occurred before the start bit was found.

Figure 1-14. Start Bit Search Example 1

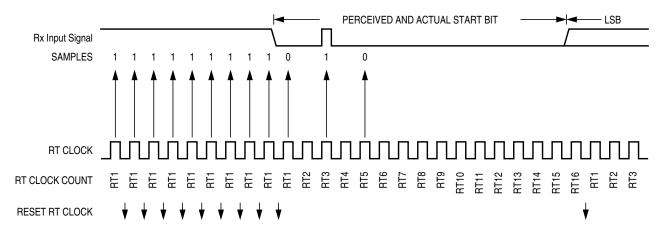

In Figure 1-15, verification sample at RT3 is high. The RT3 sample sets the noise flag. Although the perceived bit time is misaligned, the data samples RT8, RT9, and RT10 are within the bit time and data recovery is successful.

Figure 1-15. Start Bit Search Example 2

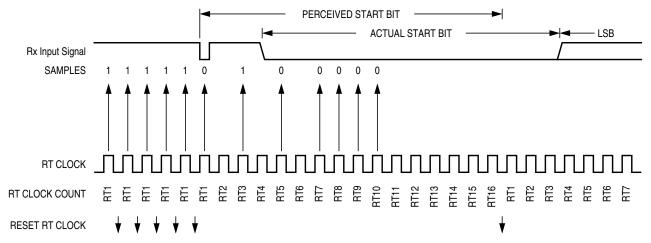

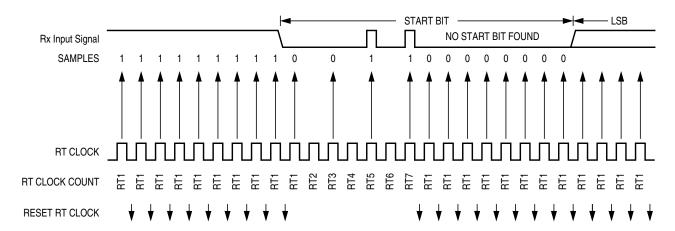

In Figure 1-16, a large burst of noise is perceived as the beginning of a start bit, although the test sample at RT5 is high. The RT5 sample sets the noise flag. Although this is a worst-case misalignment of perceived bit time, the data samples RT8, RT9, and RT10 are within the bit time and data recovery is successful.

Figure 1-16. Start Bit Search Example 3

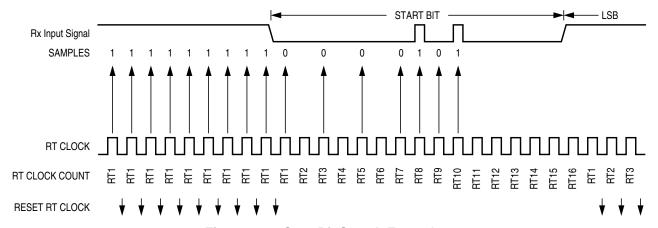

Figure 1-17 shows the effect of noise early in the start bit time. Although this noise does not affect proper synchronization with the start bit time, it does set the noise flag.

Figure 1-17. Start Bit Search Example 4

Figure 1-18 shows a burst of noise near the beginning of the start bit that resets the RT clock. The sample after the reset is low but is not preceded by three high samples that would qualify as a falling edge. Depending on the timing of the start bit search and on the data, the frame may be missed entirely or it may set the framing error flag.

Figure 1-18. Start Bit Search Example 5

In Figure 1-19, a noise burst makes the majority of data samples RT8, RT9, and RT10 high. This sets the noise flag but does not reset the RT clock. In start bits only, the RT8, RT9, and RT10 data samples are ignored.

Figure 1-19. Start Bit Search Example 6

## 1.4.4.4 Framing Errors

If the data recovery logic does not detect a logic 1 where the stop bit should be in an incoming frame, it sets the framing error flag, FE, in SCI status register 1 (SCISR1). A break character also sets the FE flag because a break character has no stop bit. The FE flag is set at the same time that the RDRF flag is set.

#### 1.4.4.5 Baud Rate Tolerance

A transmitting device may be operating at a baud rate below or above the receiver baud rate. Accumulated bit time misalignment can cause one of the three stop bit data samples (RT8, RT9, and RT10) to fall outside the actual stop bit. A noise error will occur if the RT8, RT9, and RT10 samples are not all the same logical values. A framing error will occur if the receiver clock is misaligned in such a way that the majority of the RT8, RT9, and RT10 stop bit samples are a logic zero.

As the receiver samples an incoming frame, it re-synchronizes the RT clock on any valid falling edge within the frame. Re synchronization within frames will correct a misalignment between transmitter bit times and receiver bit times.

#### 1.4.4.5.1 Slow Data Tolerance

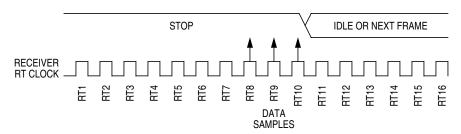

Figure 1-20 shows how much a slow received frame can be misaligned without causing a noise error or a framing error. The slow stop bit begins at RT8 instead of RT1 but arrives in time for the stop bit data samples at RT8, RT9, and RT10.

Figure 1-20. Slow Data

Let's take RTr as receiver RT clock and RTt as transmitter RT clock.

For an 8-bit data character, it takes the receiver 9 bit times x 16 RTr cycles +7 RTr cycles =151 RTr cycles to start data sampling of the stop bit.

With the misaligned character shown in Figure 1-20, the receiver counts 151 RTr cycles at the point when the count of the transmitting device is 9 bit times x 16 RTt cycles = 144 RTt cycles.

The maximum percent difference between the receiver count and the transmitter count of a slow 8-bit data character with no errors is:

$$((151 - 144) / 151) \times 100 = 4.63\%$$

For a 9-bit data character, it takes the receiver 10 bit times x 16 RTr cycles + 7 RTr cycles = 167 RTr cycles to start data sampling of the stop bit.

With the misaligned character shown in Figure 1-20, the receiver counts 167 RTr cycles at the point when the count of the transmitting device is 10 bit times  $\times$  16 RTt cycles = 160 RTt cycles.

The maximum percent difference between the receiver count and the transmitter count of a slow 9-bit character with no errors is:

$$((167 - 160) / 167) \times 100 = 4.19\%$$

#### 1.4.4.5.2 Fast Data Tolerance

Figure 1-21 shows how much a fast received frame can be misaligned. The fast stop bit ends at RT10 instead of RT16 but is still sampled at RT8, RT9, and RT10.

Figure 1-21. Fast Data

For an 8-bit data character, it takes the receiver 9 bit times x 16 RTr cycles + 10 RTr cycles = 154 RTr cycles to finish data sampling of the stop bit.

With the misaligned character shown in Figure 1-21, the receiver counts 154 RTr cycles at the point when the count of the transmitting device is 10 bit times x 16 RTt cycles = 160 RTt cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 8-bit character with no errors is:

$$((160 - 154) / 160) \times 100 = 3.75\%$$

For a 9-bit data character, it takes the receiver 10 bit times x 16 RTr cycles + 10 RTr cycles = 170 RTr cycles to finish data sampling of the stop bit.

With the misaligned character shown in Figure 1-21, the receiver counts 170 RTr cycles at the point when the count of the transmitting device is 11 bit times  $\times$  16 RTt cycles = 176 RTt cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 9-bit character with no errors is:

$$((176 - 170) / 176) \times 100 = 3.40\%$$

# 1.4.4.6 Receiver Wakeup

To enable the SCI to ignore transmissions intended only for other receivers in multiple-receiver systems, the receiver can be put into a standby state. Setting the receiver wakeup bit, RWU, in SCI control register 2 (SCICR2) puts the receiver into standby state during which receiver interrupts are disabled. The SCI will still load the receive data into the SCIDRH/L registers, but it will not set the RDRF flag.

The transmitting device can address messages to selected receivers by including addressing information in the initial frame or frames of each message.

The WAKE bit in SCI control register 1 (SCICR1) determines how the SCI is brought out of the standby state to process an incoming message. The WAKE bit enables either idle line wakeup or address mark wakeup.

## 1.4.4.6.1 Idle Input Line Wakeup (WAKE = 0)

In this wakeup method, an idle condition on the **Rx Input** signal clears the RWU bit and wakes up the SCI. The initial frame or frames of every message contain addressing information. All receivers evaluate the addressing information, and receivers for which the message is addressed process the frames that follow. Any receiver for which a message is not addressed can set its RWU bit and return to the standby state. The RWU bit remains set and the receiver remains on standby until another idle character appears on the **Rx Input** signal.

Idle line wakeup requires that messages be separated by at least one idle character and that no message contains idle characters.

The idle character that wakes a receiver does not set the receiver idle bit, IDLE, or the receive data register full flag, RDRF.

The idle line type bit, ILT, determines whether the receiver begins counting logic 1s as idle character bits after the start bit or after the stop bit. ILT is in SCI control register 1 (SCICR1).

## 1.4.4.6.2 Address Mark Wakeup (WAKE = 1)

In this wakeup method, a logic 1 in the most significant bit (msb) position of a frame clears the RWU bit and wakes up the SCI. The logic 1 in the msb position marks a frame as an address frame that contains addressing information. All receivers evaluate the addressing information, and the receivers for which the message is addressed process the frames that follow. Any receiver for which a message is not addressed can set its RWU bit and return to the standby state. The RWU bit remains set and the receiver remains on standby until another address frame appears on the **Rx Input** signal.

The logic 1 msb of an address frame clears the receiver's RWU bit before the stop bit is received and sets the RDRF flag.

Address mark wakeup allows messages to contain idle characters but requires that the msb be reserved for use in address frames. {sci\_wake}

#### NOTE

With the WAKE bit clear, setting the RWU bit after the **Rx Input** signal has been idle can cause the receiver to wake up immediately.

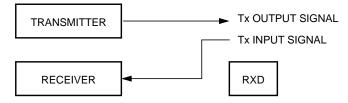

## 1.4.5 Single-Wire Operation

Normally, the SCI uses two pins for transmitting and receiving. In single-wire operation, the RXD pin is disconnected from the SCI. The SCI uses the TXD pin for both receiving and transmitting.

Figure 1-22. Single-Wire Operation (LOOPS = 1, RSRC = 1)

Enable single-wire operation by setting the LOOPS bit and the receiver source bit, RSRC, in SCI control register 1 (SCICR1). Setting the LOOPS bit disables the path from the **Rx Input** signal to the receiver. Setting the RSRC bit connects the receiver input to the output of the TXD pin driver. Both the transmitter and receiver must be enabled (TE = 1 and RE = 1). The TXDIR bit (SCISR2[1]) determines whether the TXD pin is going to be used as an input (TXDIR = 0) or an output (TXDIR = 1) in this mode of operation.

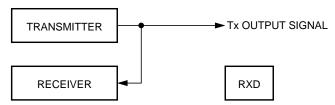

## 1.4.6 Loop Operation

In loop operation the transmitter output goes to the receiver input. The **Rx Input** signal is disconnected from the SCI

Figure 1-23. Loop Operation (LOOPS = 1, RSRC = 0)

Enable loop operation by setting the LOOPS bit and clearing the RSRC bit in SCI control register 1 (SCICR1). Setting the LOOPS bit disables the path from the **Rx Input** signal to the receiver. Clearing the RSRC bit connects the transmitter output to the receiver input. Both the transmitter and receiver must be enabled (TE = 1 and RE = 1).

## 1.5 Initialization Information

#### 1.5.1 Reset Initialization

The reset state of each individual bit is listed in Section 1.3, "Memory Map and Registers" which details the registers and their bit fields. All special functions or modes which are initialized during or just following reset are described within this section.

# 1.5.2 Interrupt Operation

# 1.5.2.1 System Level Interrupt Sources

There are five interrupt sources that can generate an SCI interrupt in to the CPU. They are listed in Table 1-14.

**Table 1-14. SCI Interrupt Source**

| Interrupt Source | Flag | Local Enable |

|------------------|------|--------------|

| Transmitter      | TDRE | TIE          |

| Transmitter      | TC   | TCIE         |

| Receiver         | RDRF | RIE          |

|                  | OR   |              |

| Receiver         | IDLE | ILIE         |

## 1.5.2.2 Interrupt Descriptions

The SCI only originates interrupt requests. The following is a description of how the SCI makes a request and how the MCU should acknowledge that request. The interrupt vector offset and interrupt number are chip dependent. The SCI only has a single interrupt line (**SCI Interrupt Signal**, active high operation) and all the following interrupts, when generated, are ORed together and issued through that port.

## 1.5.2.2.1 TDRE Description

The TDRE interrupt is set high by the SCI when the transmit shift register receives a byte from the SCI data register. A TDRE interrupt indicates that the transmit data register (SCIDRH/L) is empty and that a new byte can be written to the SCIDRH/L for transmission. Clear TDRE by reading SCI status register 1 with TDRE set and then writing to SCI data register low (SCIDRL).

#### 1.5.2.2.2 TC Description

The TC interrupt is set by the SCI when a transmission has been completed. A TC interrupt indicates that there is no transmission in progress. TC is set high when the TDRE flag is set and no data, preamble, or break character is being transmitted. When TC is set, the TXD pin becomes idle (logic 1). Clear TC by reading SCI status register 1 (SCISR1) with TC set and then writing to SCI data register low (SCIDRL).TC is cleared automatically when data, preamble, or break is queued and ready to be sent.

## 1.5.2.2.3 RDRF Description

The RDRF interrupt is set when the data in the receive shift register transfers to the SCI data register. A RDRF interrupt indicates that the received data has been transferred to the SCI data register and that the byte can now be read by the MCU. The RDRF interrupt is cleared by reading the SCI status register one (SCISR1) and then reading SCI data register low (SCIDRL).

#### 1.5.2.2.4 OR Description

The OR interrupt is set when software fails to read the SCI data register before the receive shift register receives the next frame. The newly acquired data in the shift register will be lost in this case, but the data already in the SCI data registers is not affected. The OR interrupt is cleared by reading the SCI status register one (SCISR1) and then reading SCI data register low (SCIDRL).

## 1.5.2.3 IDLE Description

The IDLE interrupt is set when 10 consecutive logic 1s (if M=0) or 11 consecutive logic 1s (if M=1) appear on the receiver input. Once the IDLE is cleared, a valid frame must again set the RDRF flag before an idle condition can set the IDLE flag. Clear IDLE by reading SCI status register 1 (SCISR1) with IDLE set and then reading SCI data register low (SCIDRL).

# 1.5.3 Recovery from Wait Mode

The SCI interrupt request can be used to bring the CPU out of wait mode.